Testing and locating method for FPGA (field programmable gate array) programmable logic unit

A positioning method and programming logic technology, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve problems such as short time, achieve the effect of realizing error positioning and improving test efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

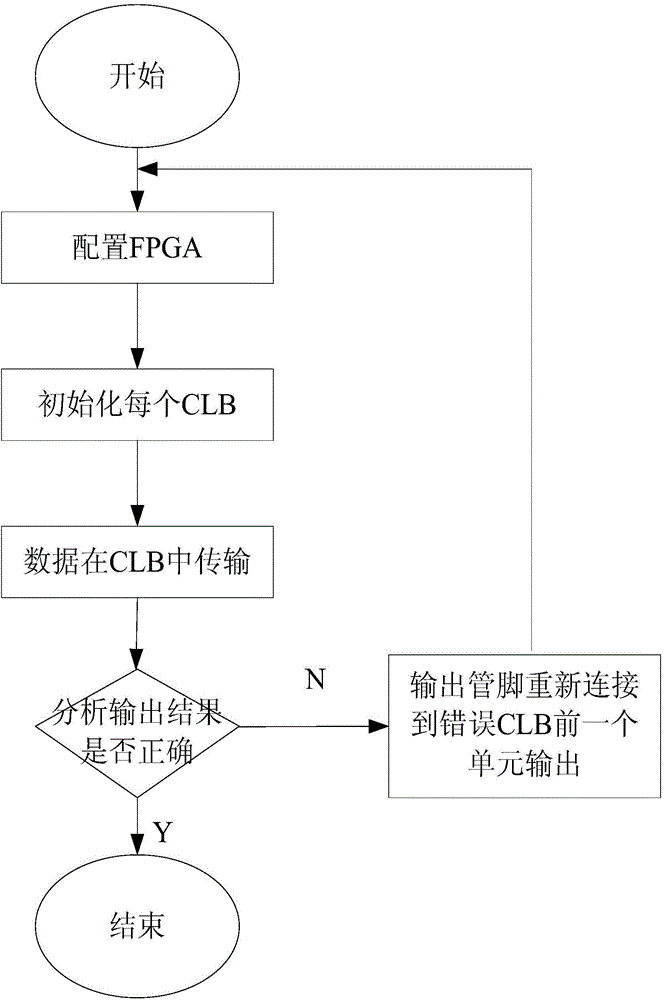

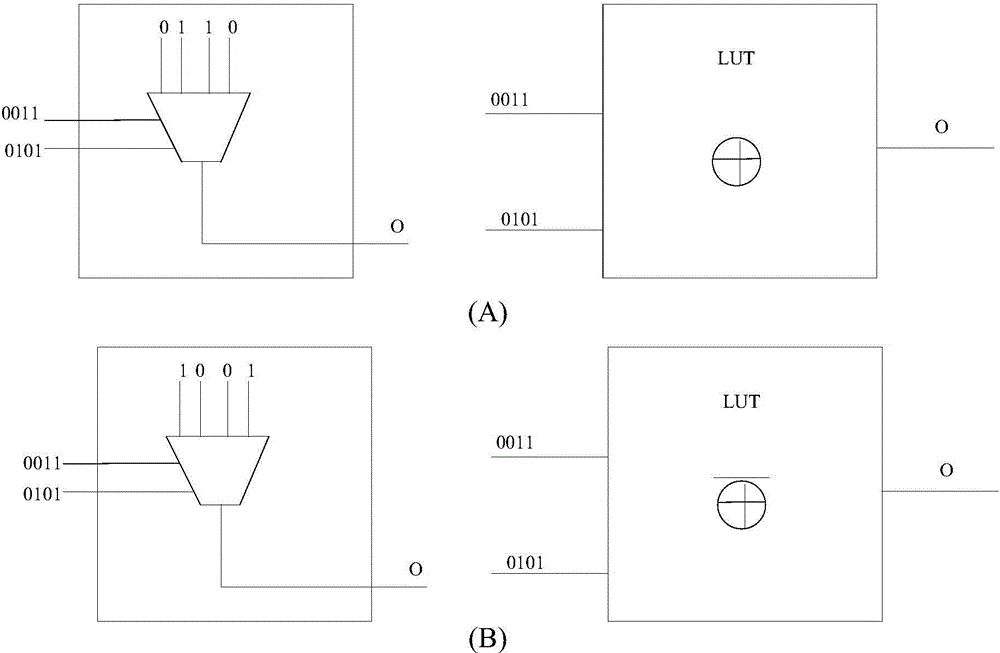

[0023] In order to facilitate the understanding of the technical solutions of the present invention, the following will be introduced in conjunction with specific implementation methods, such as figure 1 It is a flowchart of the technical solution of the present invention, and the specific steps are as follows: (1) arrange and configure the FPGA logic unit; the specific arrangement and configuration method is: the CLB modules of the FPGA to be tested are arranged in parallel into a plurality of one-dimensional CLB arrays, and the F-LUT For example, all F-LUTs and DFF modules in CLB are configured as a shift serial chain, and its input signal is the common input terminal of F1-F3 of all F-LUTs in FPGA, which is a parallel input signal; F4 of F-LUT It is a serial input port, F4 of the first CLB of each row of CLB is connected to the input signal port, F4 ports of other CLB units are connected to the DFF output signal Y1 of the previous CLB; c1 of the first CLB of each row of CLB ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com