Method for testing small delay defects based on normalization delay probability distribution

A technology of delay probability and defect testing, which is applied in the direction of electronic circuit testing, etc., can solve problems such as test vector omission, small delay defect test effectiveness impact, etc., to achieve the effect of reducing generation time and improving effectiveness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] The small delay defect testing method based on the normalized delay probability distribution provided by the present invention will be described in detail below in conjunction with the accompanying drawings, but this does not constitute a limitation to the present invention.

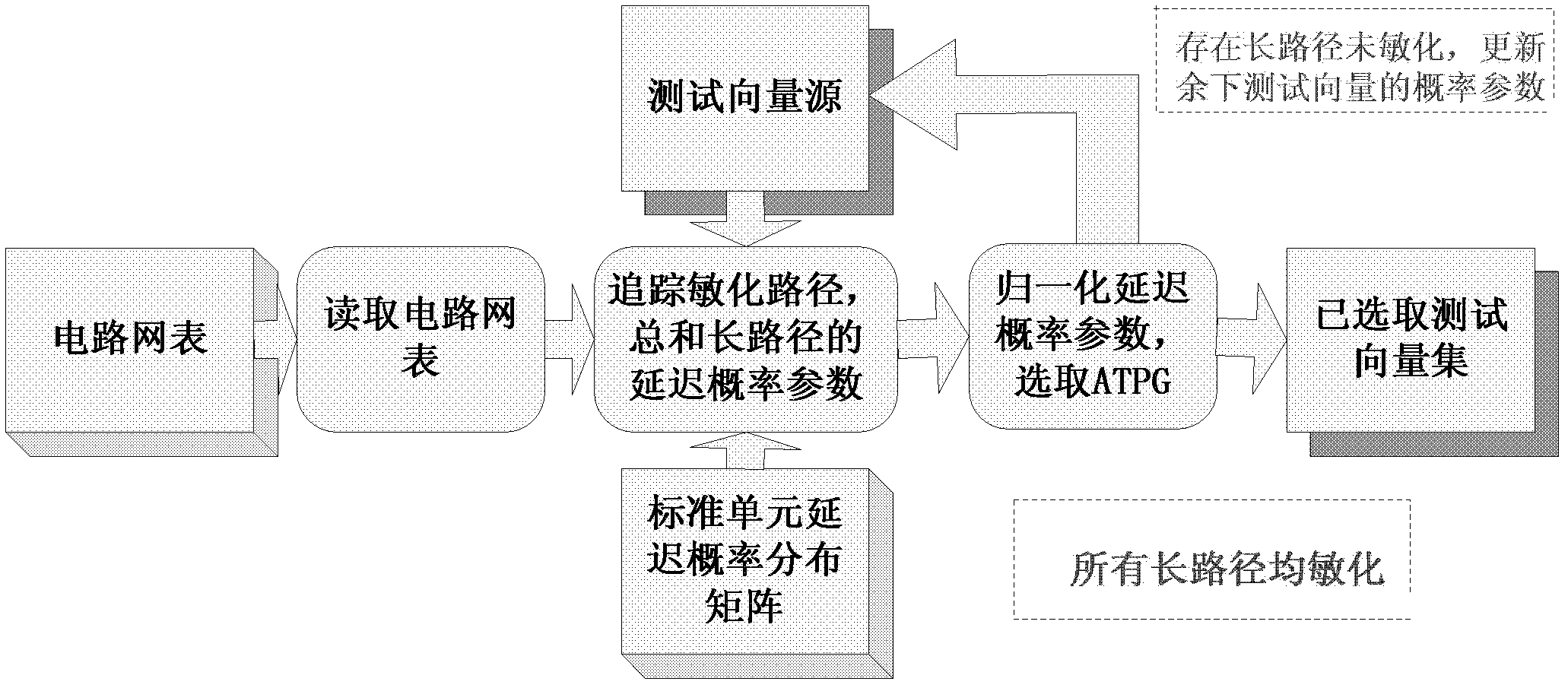

[0014] The present invention is based on the small delay defect testing method of normalized delay probability distribution, and its steps include:

[0015] Phase 1: Establishment of standard unit delay probability distribution matrix

[0016] Step1: Synthesize the circuit under test (DUT) with the Design Compiler tool, and extract the driver and load information of the standard unit;

[0017] Step2: According to the design specifications, use the Specter tool to build a standard cell with drive and load properties (including all standard cells required for Design Compiler synthesis), and set the process fluctuation range and process matching characteristics, and do 200 times of Monte Carlo of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com