Erasing method for flash memory

A flash memory, over-erasing technology, applied in static memory, read-only memory, information storage, etc., can solve problems such as affecting erasure verification, wasting time, etc., and achieve the effect of shortening erasing time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

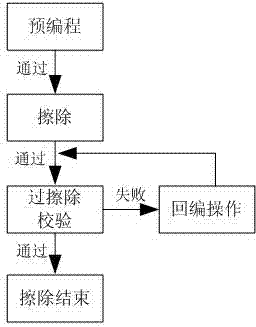

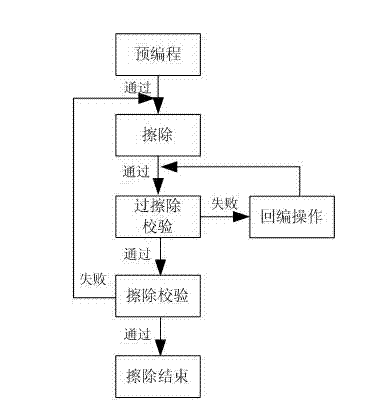

[0030] based on the following Figure 4 , specify the preferred embodiment of the present invention:

[0031] Such as Figure 4 Shown is a flow chart of a method for erasing a flash memory provided by the present invention, and the method for erasing a flash memory includes the following steps:

[0032] Step 1. Pre-program verification. If any cell is in the erased state, perform pre-programming on the cell.

[0033] Pre-programming is pre-programming for each unit in a sector (sector) or block (block).

[0034] Step 2. Clear the erase flag bit.

[0035] Step 3. Perform erasure verification internally. If the verification fails, go to step 4. If the verification passes, go to step 5;

[0036] Step 4. Perform an erase operation on the sector or block in the under-erased state, set the erase flag to 1, and jump to step 3.

[0037] Step 5. Clear the over-erased flag bit.

[0038] Step 6, judging whether the erasing flag is zero, if yes, then jump to step 10, if not, then ju...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com