Method for realizing multi-serial-port extension by using FPGA (field programmable gate array)

A multi-serial port and serial port technology, applied in the field of serial port communication, can solve the problems of not being able to meet the diversity of user data and the inability to realize multi-serial port expansion, etc., and achieve the effects of low power consumption, convenient and flexible connection, and convenient expansion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

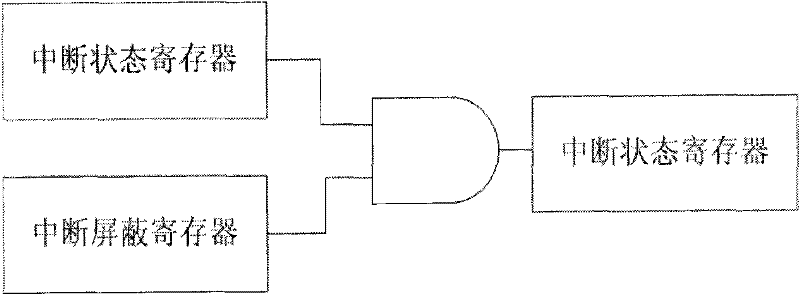

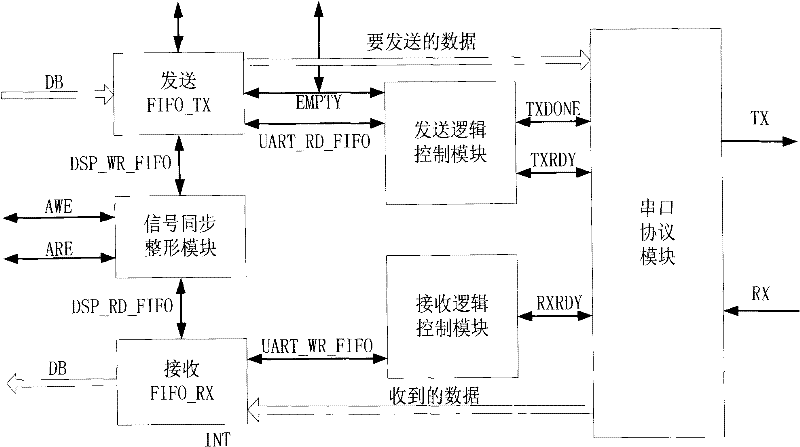

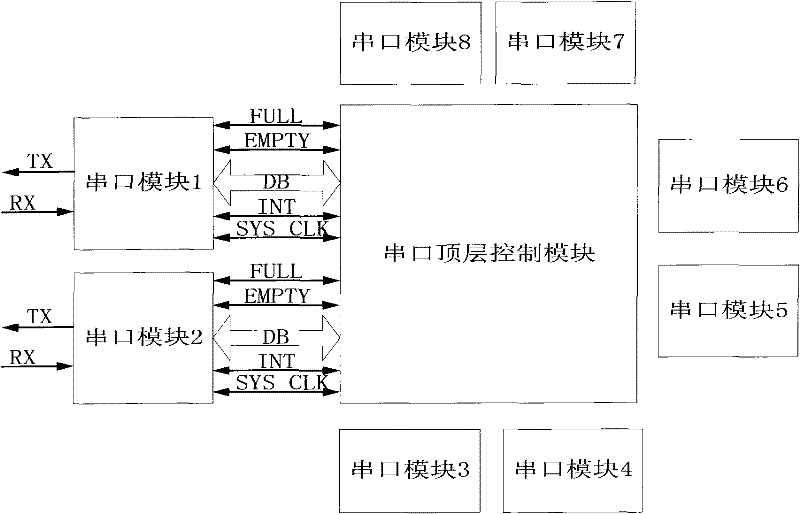

[0047] Next, according to the address allocation of registers and registers in Table 1 above, we will introduce in detail the functions and specific implementations of these registers during the interaction process.

[0048] 1) Interrupt status register (UARTINT): bit[7:0] corresponds to the interrupt status of channels 7 to 0, respectively, the corresponding bit is 5-1, indicating that the corresponding channel generates an interrupt, and 0, indicating no interrupt. The 8 serial ports can work in parallel, and there are 8 FIFOs corresponding to them in the FPGA. When an interrupt occurs, the DSP needs to know which channel sent it, so there is an interrupt status register.

[0049] 2) Interrupt depth register (S_INT_DEPTH): programmable interrupt depth, for example: writing 128 indicates that the channel receives 128 bytes and generates an interrupt. The UART converts the received data into parallel data and puts it in the FIFO. When there are as many bytes as there are, an i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com