General rapid decoding coprocessor of quasi-cyclic low density parity check code

A low-density parity and coprocessor technology, applied in the field of channel coding and decoding, can solve problems such as low decoding efficiency and scattered storage resource allocation, and achieve the effect of improving decoding efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

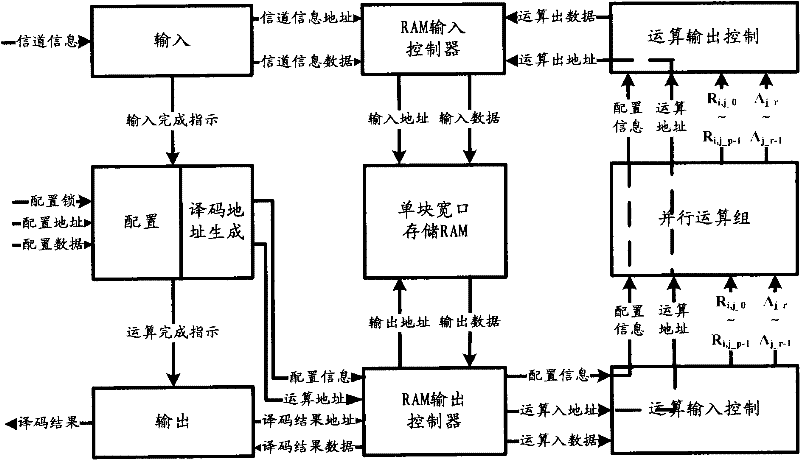

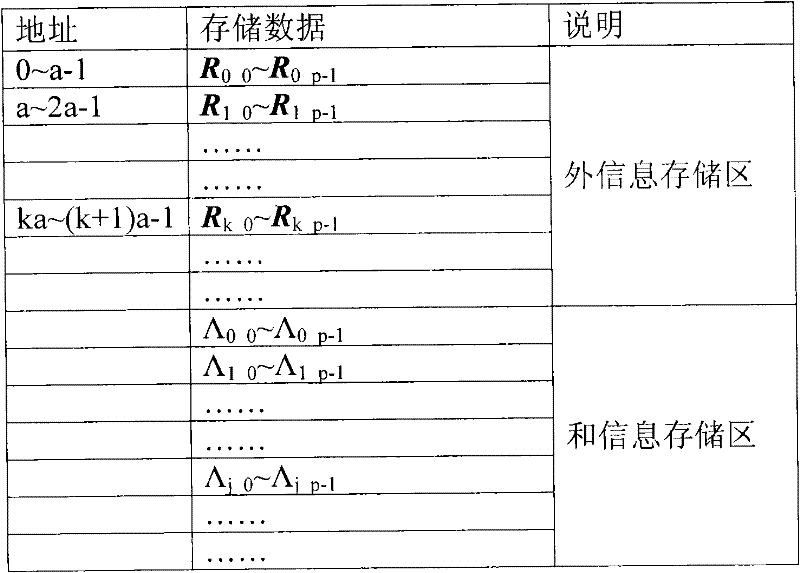

Method used

Image

Examples

Embodiment 1

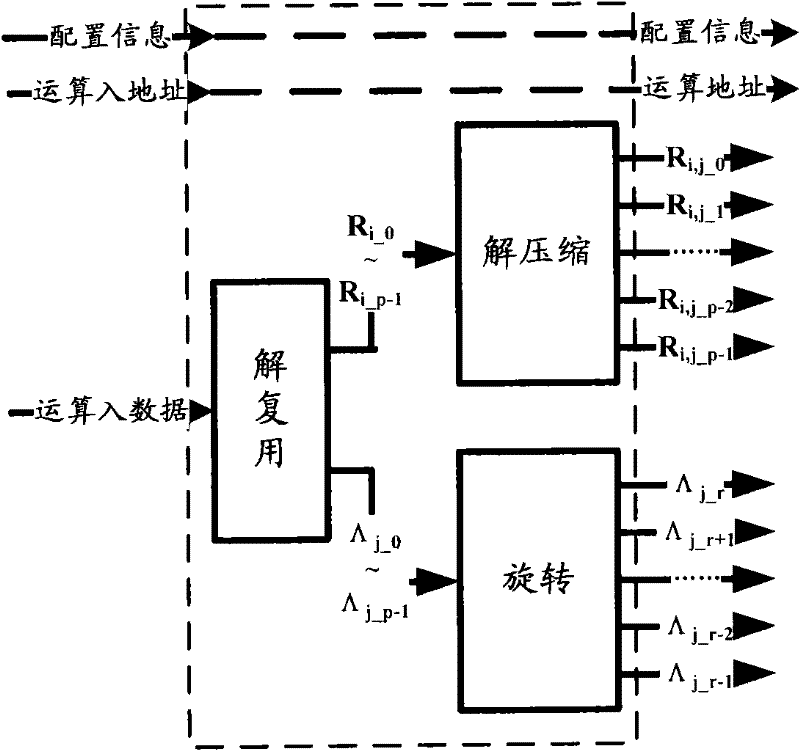

[0055] Embodiment 1: Example of a serial operator

[0056]Serial operators perform sum and product operations in serial cascade

[0057] Λ' i,j_k =Λ j_k -R i,j_k

[0058] R i , j _ k ′ = min j ′ ∈ N ( i ) \ j ( Λ i , j ′ _ k ′ )

[0059] Λ j_k = Λ' i,j_k +R i,j_k

[0060] Its structure is as Figure 5 shown. Since the serial operator can only receive one sum information at a time, its operation sh...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com