Interconnection matrix for uncompetitive electrification, configuration and reconfiguration of FPGA (Field Programmable Gate Array)

A technology of electrical configuration and reconfiguration, applied in the field of interconnect matrix, to reduce current consumption, improve stability, and avoid device burnout

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present invention will be further introduced below in conjunction with the accompanying drawings.

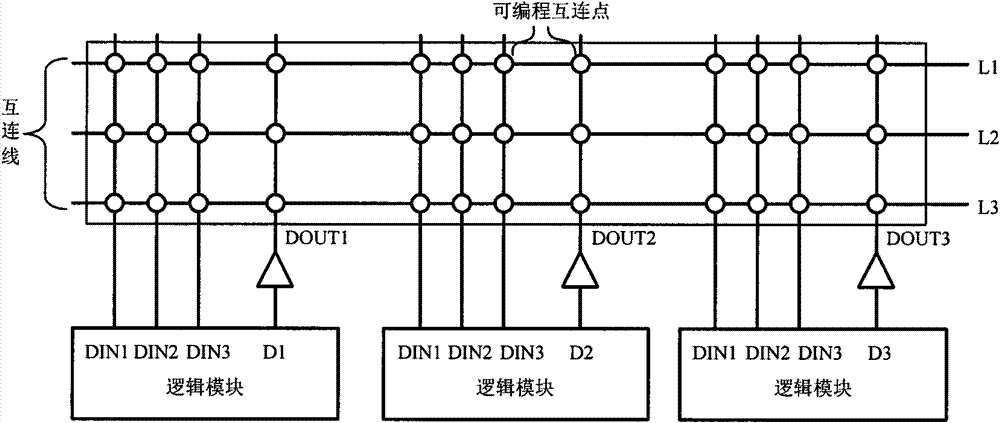

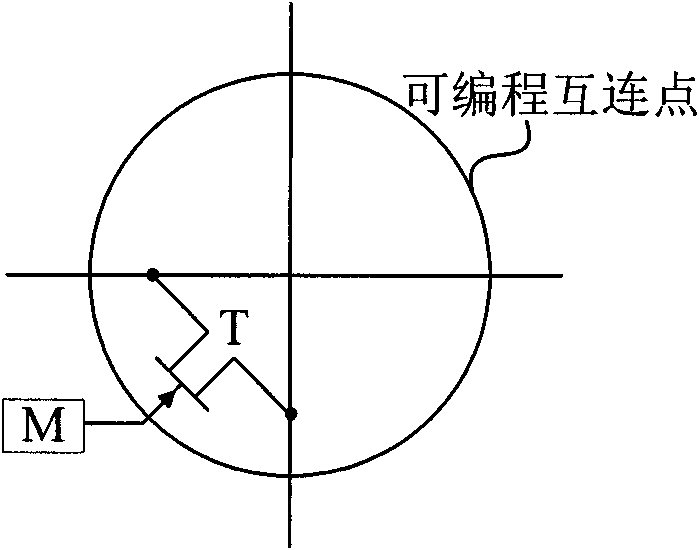

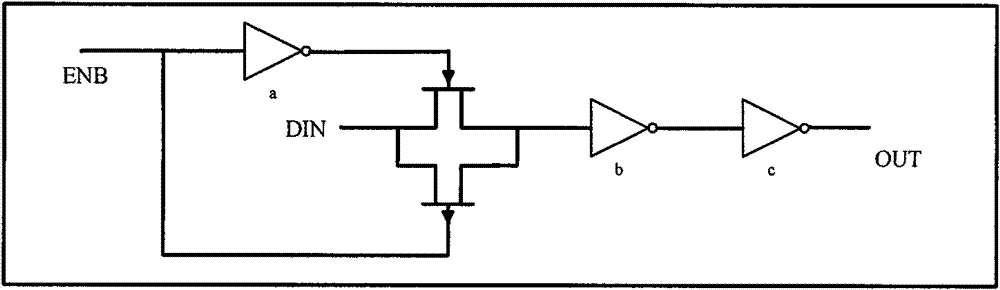

[0028] The interconnection matrix provided by the invention can eliminate the competition among the output drivers of the SRAM type FPGA in the process of power-on, configuration and reconfiguration. The interconnection matrix composed of interconnection lines and programmable interconnection points (PIPS) is an important part of FPGA. The interconnection lines are connected through programmable transmission pipes inside the programmable interconnection point (PIPS), and the programmable transmission pipes can control the connection and disconnection of these interconnection lines. Output signals from two sources, internal logic and I / O pins, are driven through the outputs, and passed through Programmable Interconnect Points (PIPS) and wires in all directions.

[0029] The non-competitive power-up, configuration and reconfiguration interconnection matrix of the prese...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com