Deleted graph-based parallel decomposition method for circuit sparse matrix in circuit simulation

A sparse matrix, circuit simulation technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of few parallel software and few parallel versions of general-purpose multi-core CPU platforms, etc., to ensure a high degree of parallelization , the effect of acceleration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

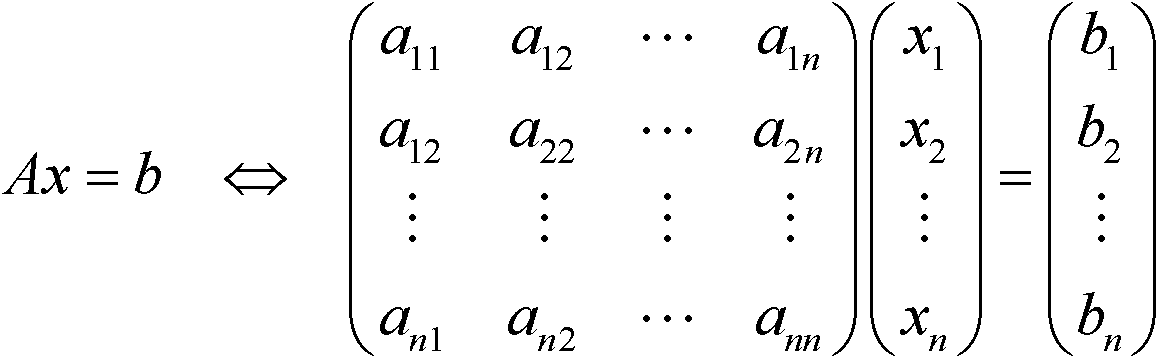

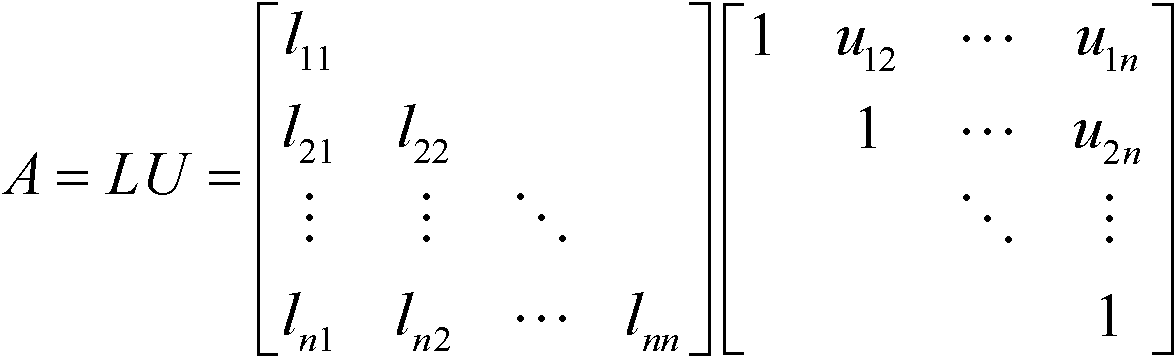

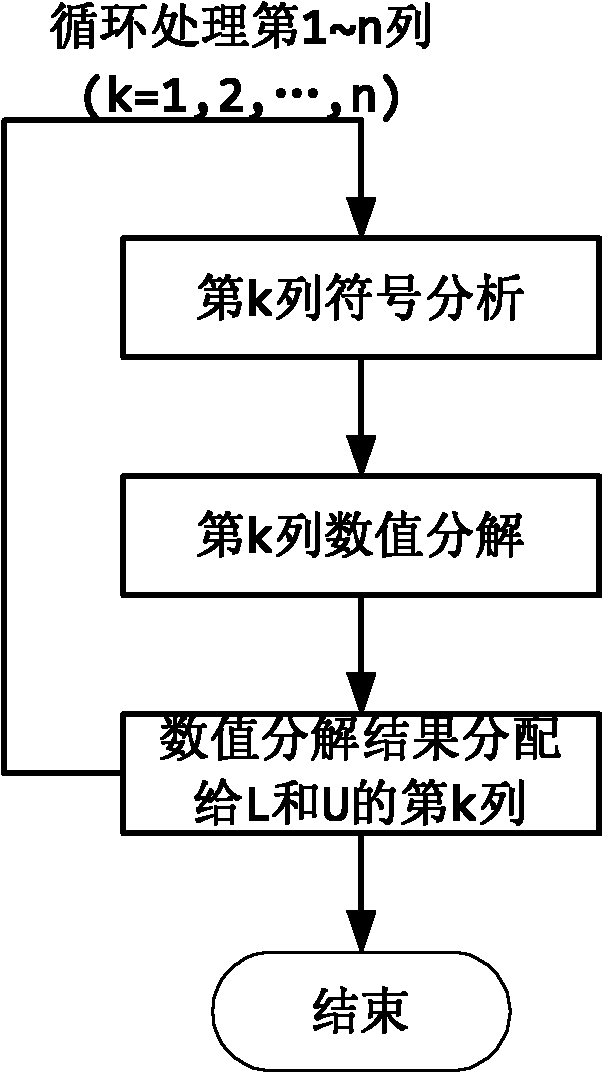

[0044] In order to achieve the above object, the present invention adopts following technical scheme, and its implementation steps are:

[0045] Step 1: Perform symbol analysis on the input n×n circuit matrix A, and complete the calculation of the non-zero element structure of n columns of L and U in sequence from the first column to the nth column;

[0046] Step 2: Utilize the non-zero structure of the U matrix obtained in step 1, and obtain the elimination graph through the earliest start algorithm;

[0047] Step 3: Based on the non-zero structure of L and U obtained in step 1 and the elimination graph obtained in step 2, perform parallel LU numerical decomposition. In the numerical decomposition process, two different parallel methods are used: group parallelism and pipeline parallelism. The two parallel methods are dynamically selected during the numerical decomposition process according to the structure of the elimination graph. Thus, the parallel LU decomposition proce...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com