Error code testing system based on FPGA (Field Programmable Gate Array)

A bit error testing and bit error technology, applied in the field of communication, can solve the problems of complex implementation structure and long synchronization time, and achieve the effect of improving flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The present invention will be further described below in conjunction with accompanying drawing and specific implementation;

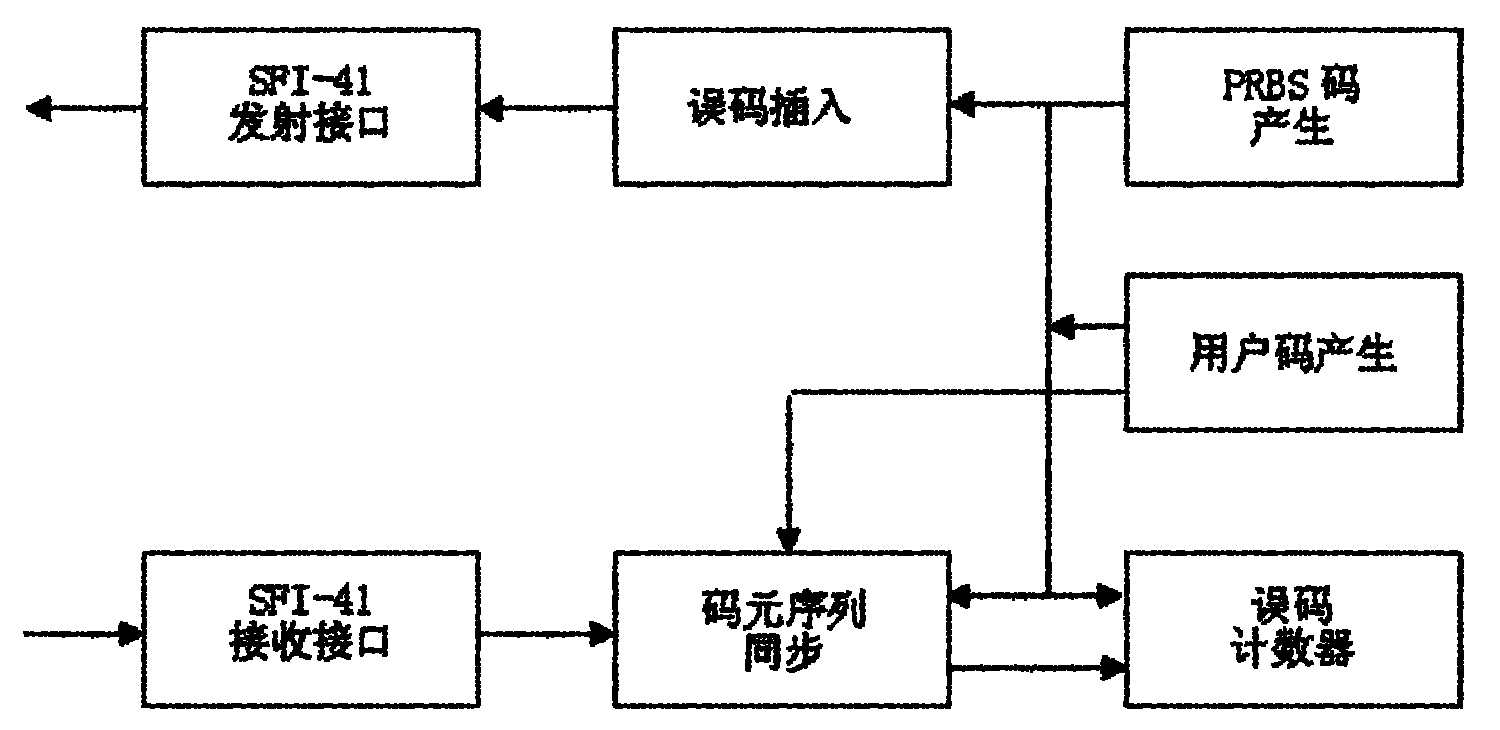

[0034] see figure 1 The functional block diagram of the FPGA bit error test is shown. It includes SFI-41 receiving interface, symbol sequence synchronization module, error counter, user code generating module, PRBS module, error inserting module and SPF-41 transmitting interface.

[0035] The symbol sequence synchronization module is used to realize the synchronization between the received symbol and the local symbol; the error counter is used to count the number of symbol errors in a certain period of time; the user code generation module is used to generate custom codes; PRBS The module generates PRBS symbols; the bit error insertion module is used for the sending end to insert bit errors into the data.

[0036] based on figure 1 In the bit error test method of FPGA shown above, high-speed data is converted to serial and parallel before ente...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com