Method for compensating deformation effect after exposure of two-dimensional design layout

A technology of graphic exposure and compensation method, which is applied in the direction of optics, photographic process of pattern surface, and originals used in photomechanical processing, etc., which can solve problems such as poor accuracy, long time consumption, and complicated compression effect process.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The technical solutions and other beneficial effects of the present invention will be apparent through the detailed description of specific embodiments of the present invention below in conjunction with the accompanying drawings.

[0027] The method for compensating the serious deformation effect after exposure of two-dimensional design graphics includes the following steps:

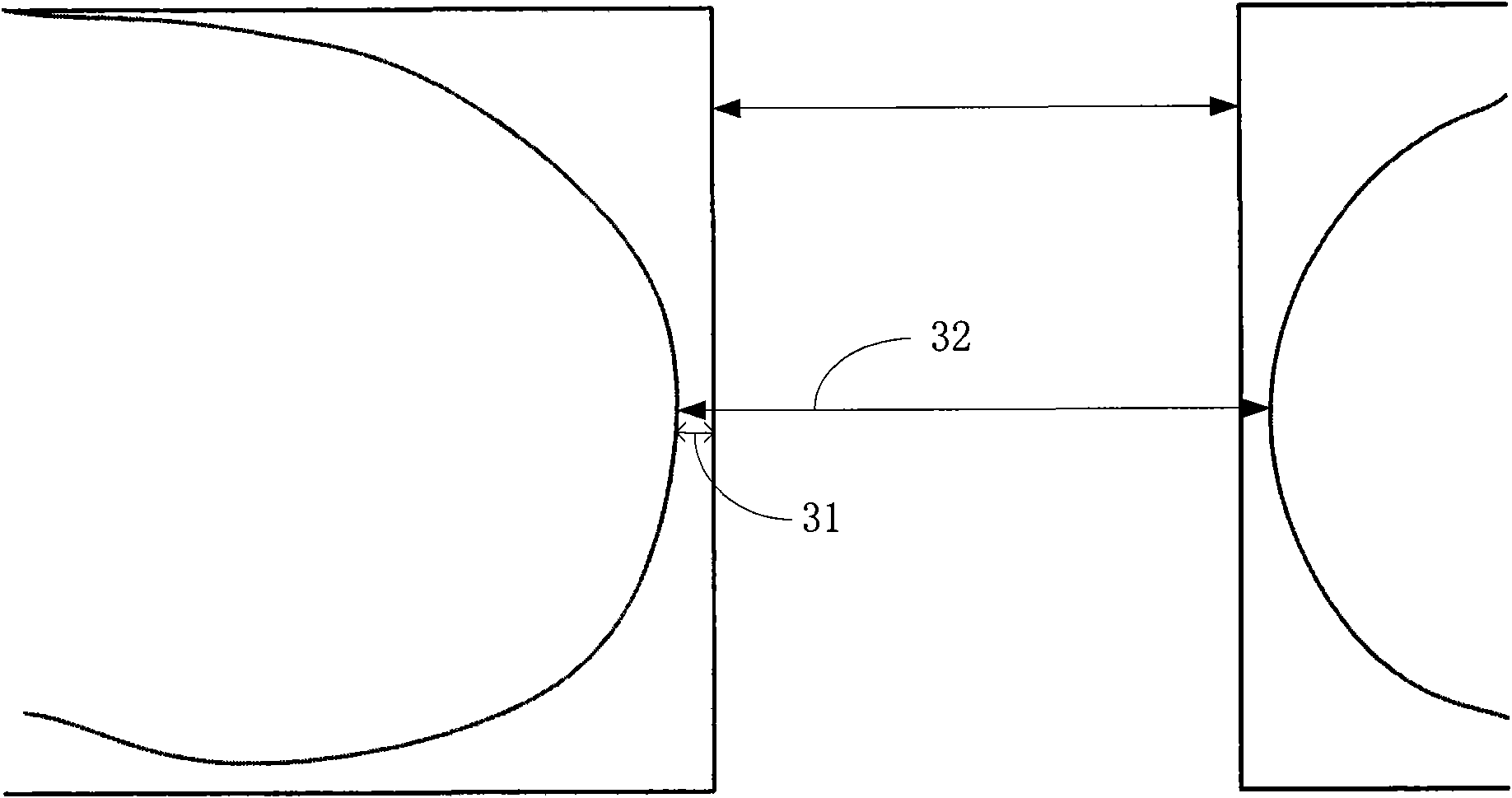

[0028] Establish a two-dimensional design graphic, and set the edge placement error of key dimensions that need to be compensated;

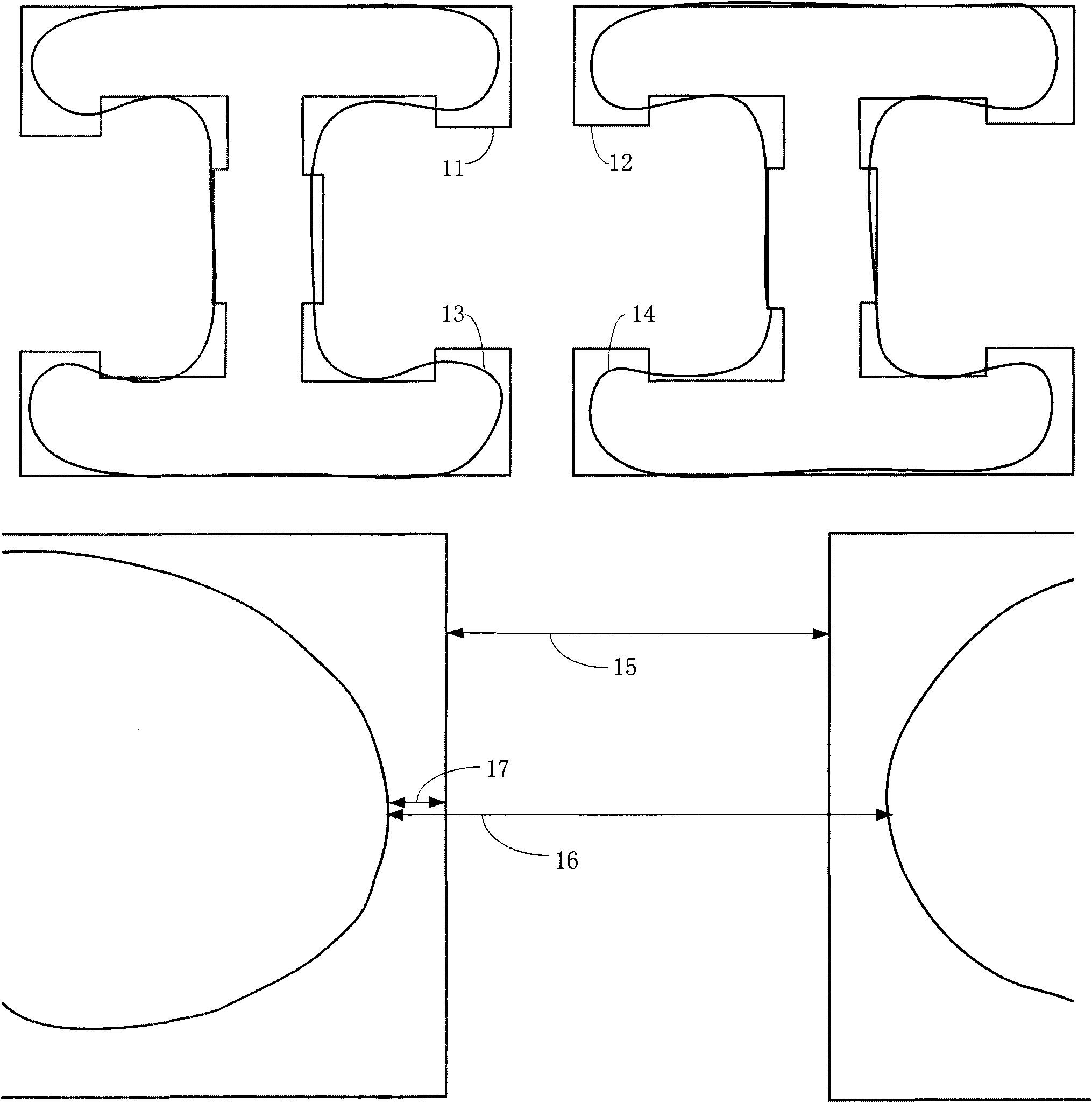

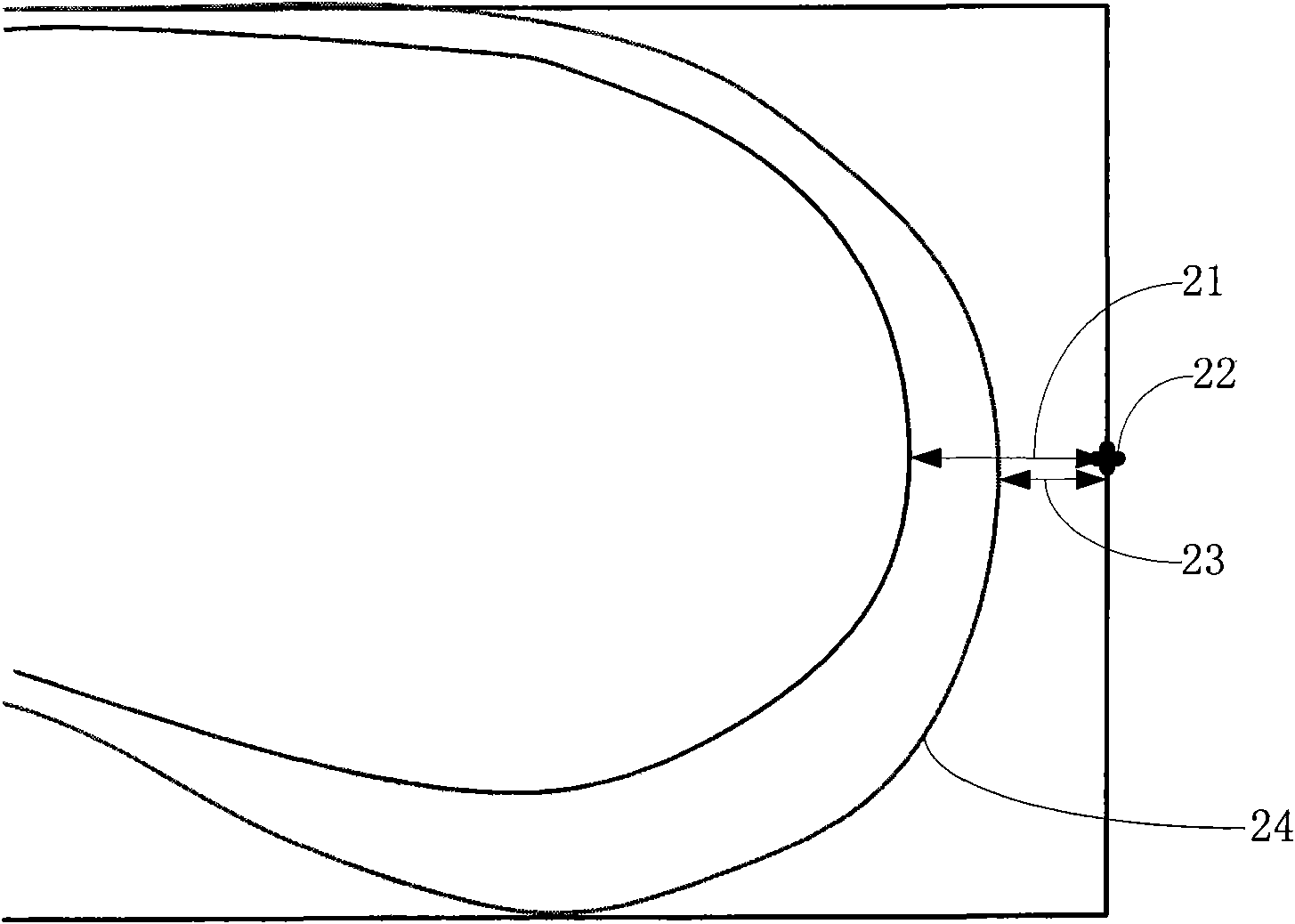

[0029] On the design graphic, first select a point (usually the center of the design graphic side) as the first sampling point, then take the sampling point at a predetermined interval (preferably 30nm) to divide the design graphic with the first sampling point;

[0030] Use the optical proximity correction technique for correction and simulation to obtain the edge placement errors of all sampling points;

[0031] A standard optical proximity correction model is est...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com