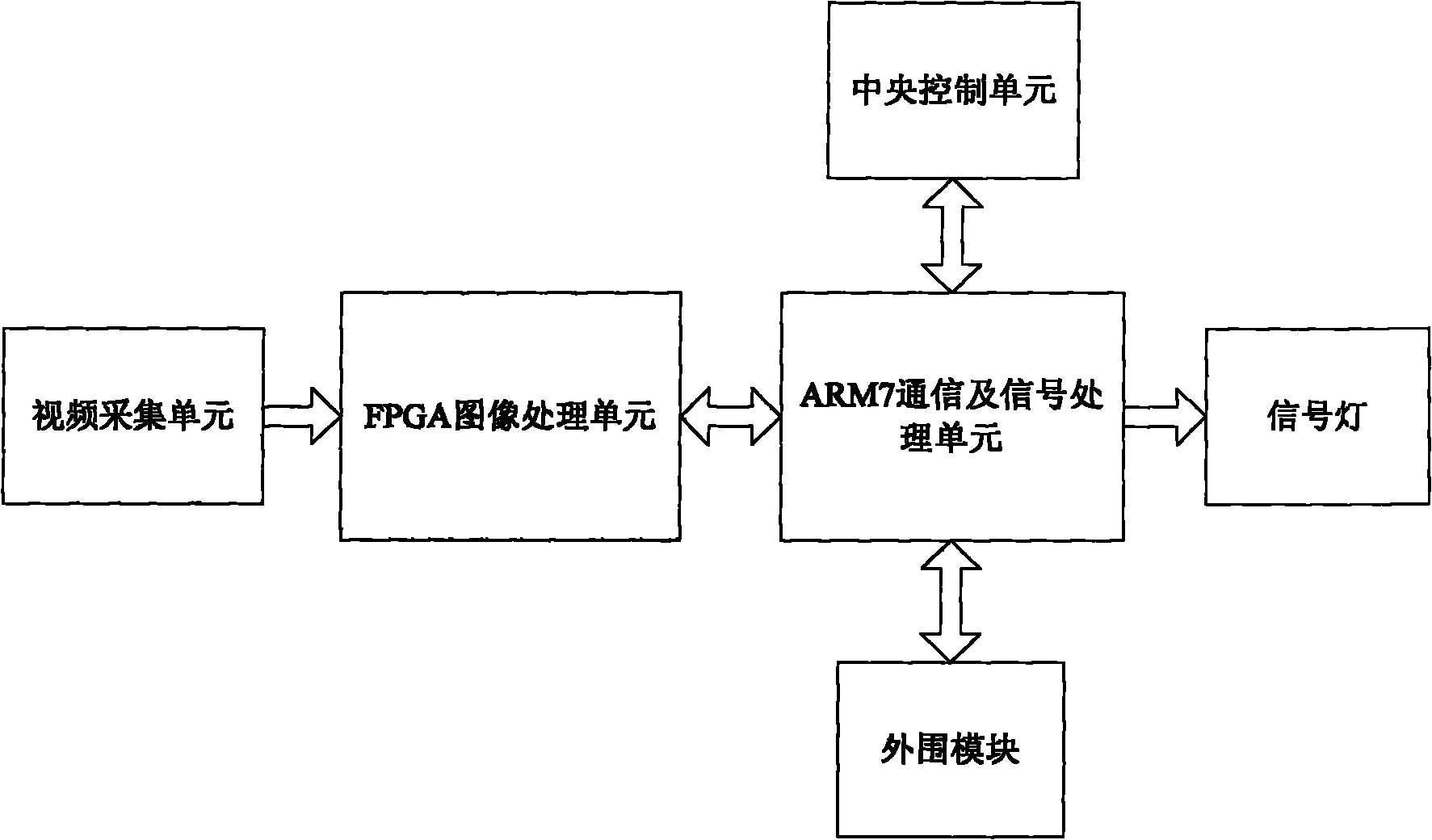

FPGA-based traffic signal control machine for intersection queue length image detection

A technology for queuing length and image detection, which is applied in traffic signal control, traffic flow detection, etc., can solve the problems of long time, poor real-time performance, and low cost, and achieve the effect of strong scalability and good real-time performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

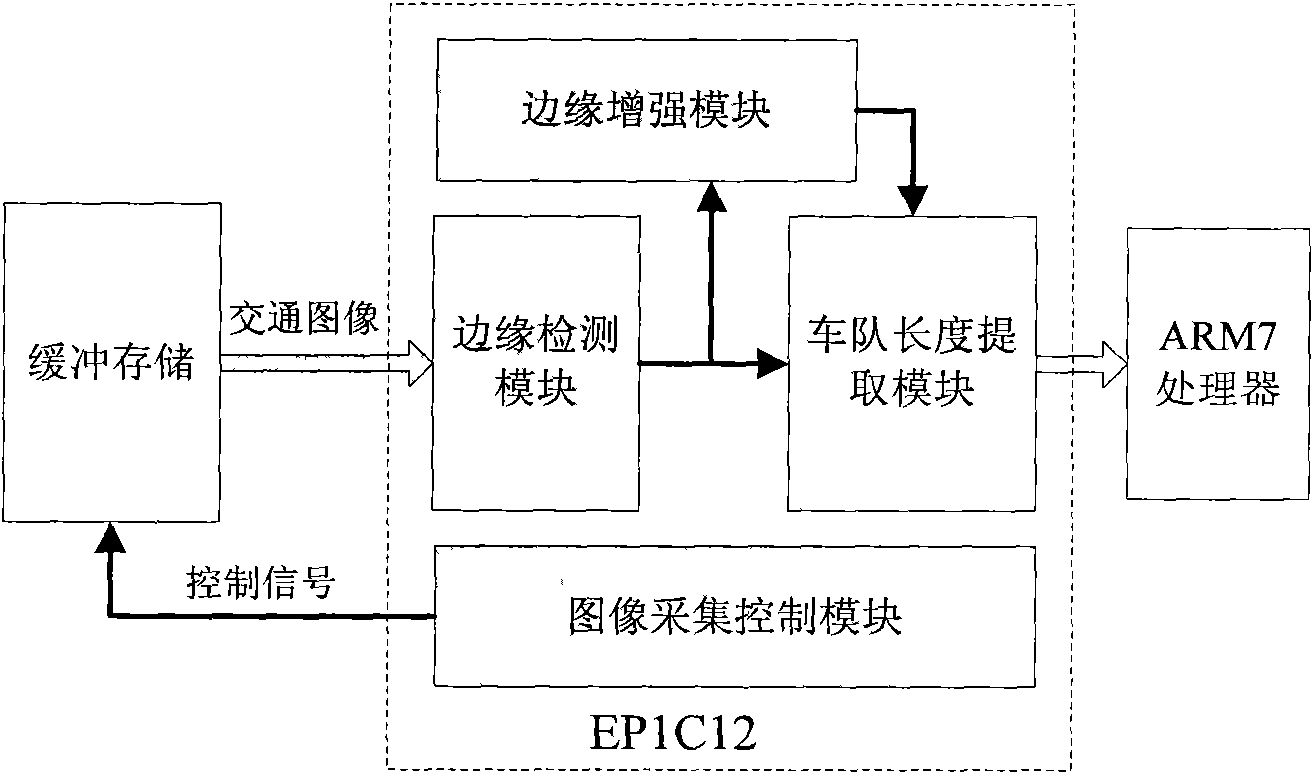

[0019] The video acquisition unit adopts CCD, which can collect the live image and send it to the A / D conversion chip for further processing. The A / D chip adopts the 7111 chip of PHILIPS Company. The 7111 chip has 4 analog channels. It collects 4 channels of image signals in time-sharing and processes them in time-sharing. The conversion mode of 7111 can be selected by programming. 2 C bus for programming, complete the initialization of 7111, the output format of the signal is also determined by I 2 The C bus is used for control, using the 4:2:2 format of CCIR601. In this way, the on-site image is converted from analog data to digital data, which can be sent to the FPGA chip for corresponding processing through the buffer.

[0020] The FPGA adopts the EP1C12 chip in the Cyclone series FPGA of Altera Company of the United States. The chip has a density of 12060 LE units (each LE includes a LUT, a flip-flop and related logic, which is the most basic structure of chip implement...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com