Method for downloading field programmable gate array (FPGA) logic codes under joint test action group (JTAG) download mode

A code and logic technology, applied in the download field of FPGA logic code under the download mode of the joint test action group, can solve the problems of inability to meet the debugging requirements of the new system, occupy other ports of the CPU, and fail to load the device, so as to improve the download efficiency, The effect of fast download speed and improved reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The present invention will be described in detail below in conjunction with the embodiments and accompanying drawings, but the present invention is not limited thereto.

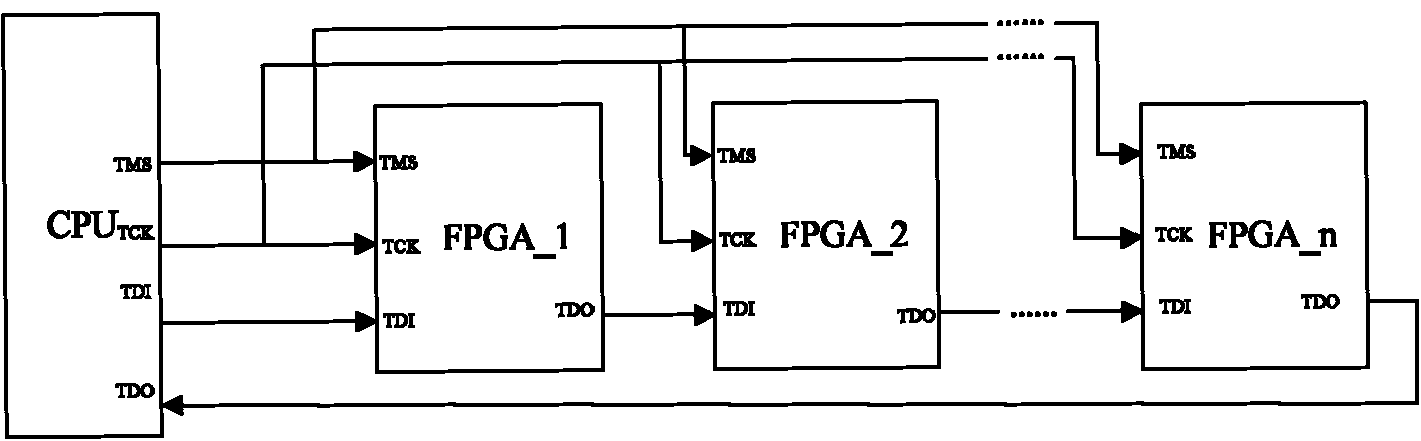

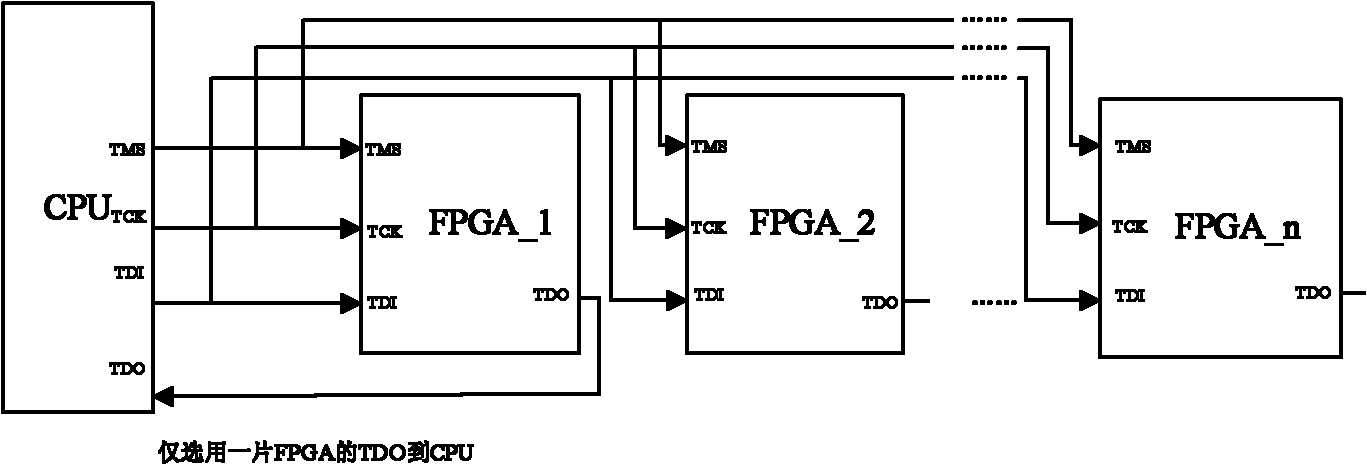

[0030] The downloading method of the present invention will be described in detail below by taking a system containing n FPGAs as an example, wherein the FPGA chip of Xilinx Company is used as an example.

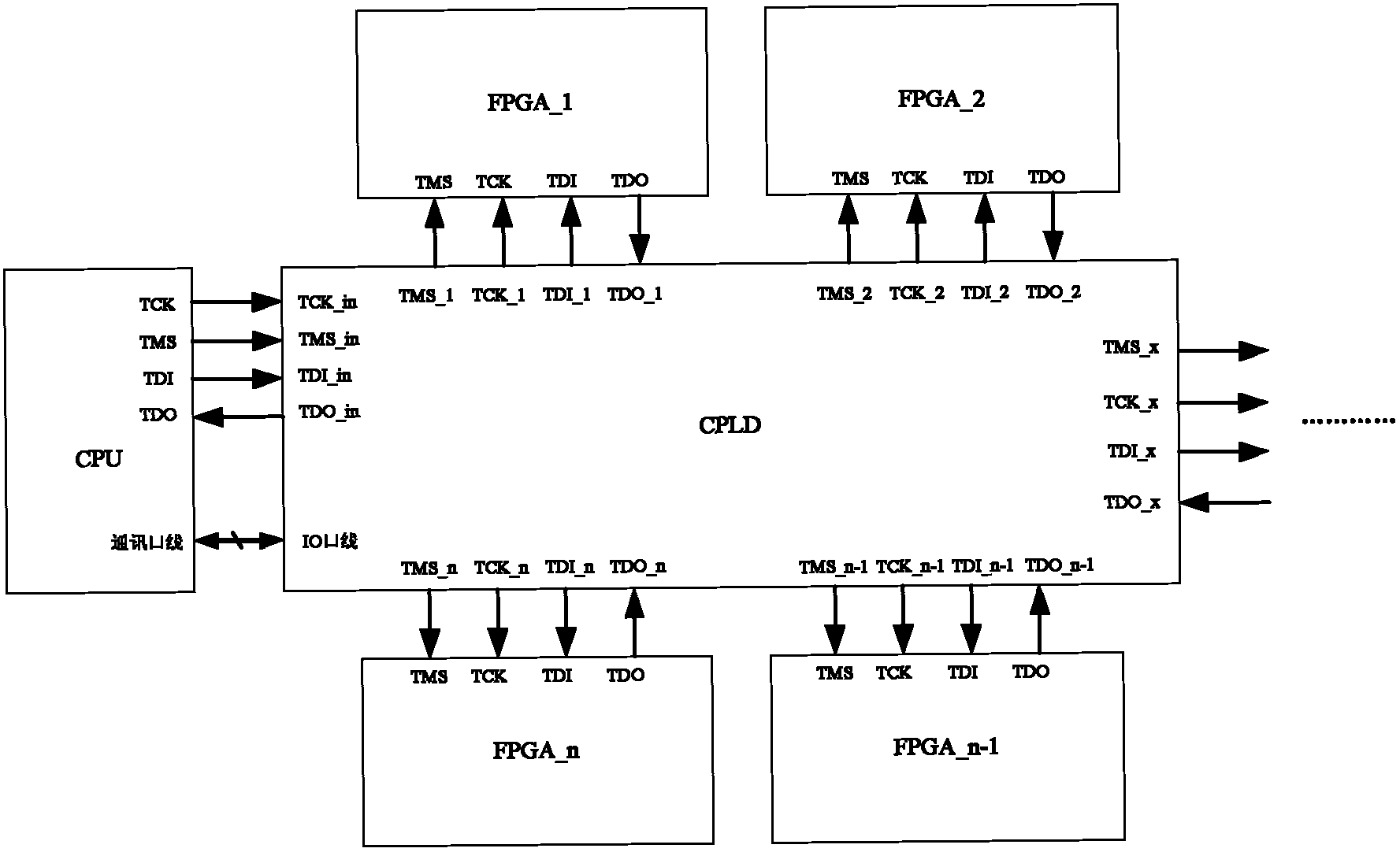

[0031] Such as image 3 As shown, a method for downloading FPGA logic codes in a JTAG download mode, including:

[0032] (1) The communication port of CPU is connected to the communication port of CPLD, forms the communication port line of CPU and CPLD, adopts I 2 C bus protocol;

[0033] Connect the TMS (test mode selection) signal, TCK (test clock input) signal, TDO (test data output) signal and TDI (test data input) signal in the JTAG download signal simulated by the CPU port to a CPLD (Complex Programmable Logic Device, complex programmable logic device);

[0034] Among them, several JTAG do...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com