Low-power consumption programmable frequency divider

A frequency divider, low power consumption technology, applied in pulse counters, counting chain pulse counters, electrical components, etc., can solve the problems of narrow frequency division ratio, large power consumption, etc., to achieve strong burr elimination ability and reduced power consumption , Programmable wide range of effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be further described below in conjunction with the accompanying drawings.

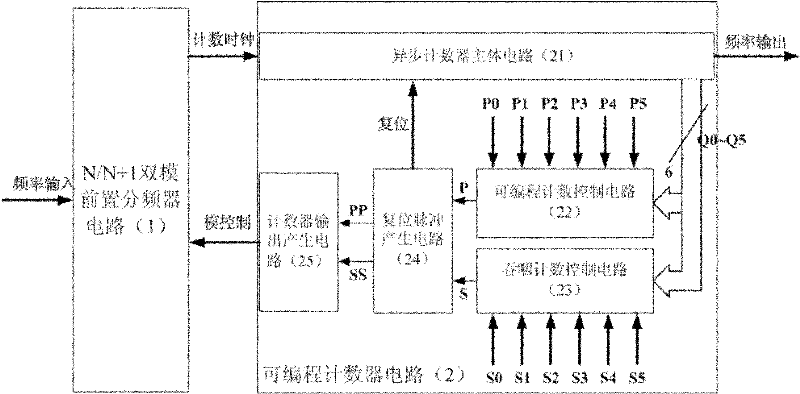

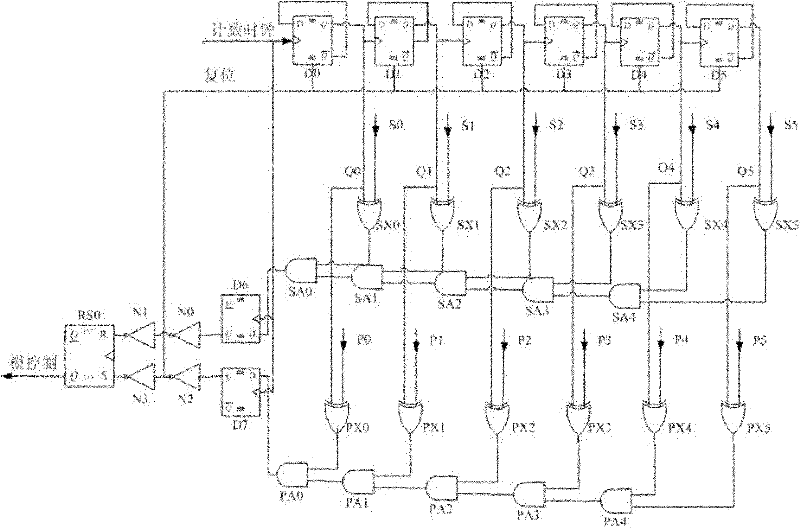

[0029] A low-power programmable frequency divider with a wide programmable range described in the present invention, on the basis of the traditional programmable frequency divider structure, combines the programmable counter and the swallowing counter into one, sharing a D The main circuit of the counter composed of flip-flop chains, figure 1 Shown is the block diagram of the programmable frequency divider of this design.

[0030] A low-power programmable frequency divider with a wide programmable range described in the present invention is mainly composed of an N / N+1 dual-mode prescaler circuit 1 and a programmable counting circuit 2 . The programmable counter circuit 2 is composed of five parts: an asynchronous counter main circuit 21 , a programmable count control circuit 22 , a swallow count control circuit 23 , a reset pulse generation circuit and a counter outp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com