Multilayer chip varistor and manufacturing method thereof

A varistor, multi-layer chip technology, applied in the direction of resistance manufacturing, varistors, resistors, etc., can solve the problems of circuit complexity, multi-line area, circuit design, maintenance hidden dangers, etc., to save installation space, The effect of reducing the size of the component

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

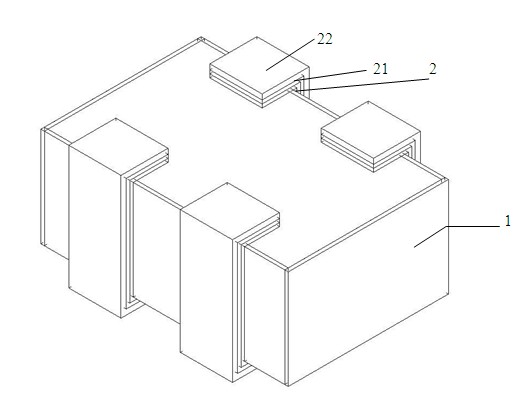

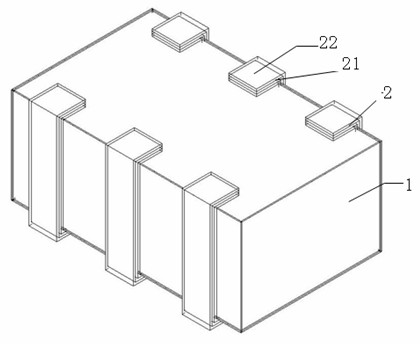

[0042] Such as Figure 1-4 As shown, the multilayer chip varistor of this embodiment includes a varistor substrate whose overall shape is a cuboid, and the varistor substrate includes a lower substrate, an upper substrate, and a substrate between the upper substrate and the lower substrate. A piezoresistor substrate consisting of multiple layers of piezoresistor units including internal electrodes and piezoresistor films. The long-height sides of the piezoresistor substrate are formed by pairwise 4, 6, or 8 terminal electrodes opposite each other. Row-shaped structure, the wide-high side of the varistor substrate has no auxiliary terminal electrodes; the internal electrodes include 2, 3 or 4 mutually independent internal electrode units, and each of the internal electrode units is connected to a pair of the Terminal connection.

[0043] The manufacturing method of the multilayer chip varistor of this embodiment includes the following steps:

[0044] (1) Preparation of slurry...

Embodiment 2

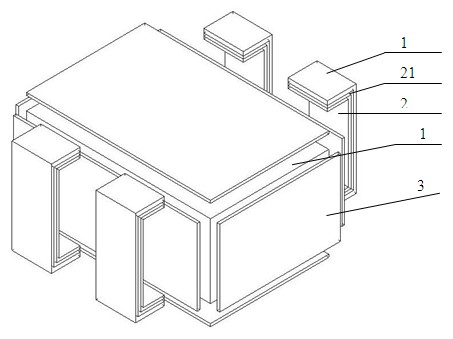

[0093] Such as Figure 5-7 As shown, the difference between the multilayer chip varistor of this embodiment and the multilayer chip varistor of Embodiment 1 is that the multilayer chip varistor of this embodiment also includes two A pair of auxiliary terminal electrodes on two wide and high sides, the auxiliary terminal electrodes are connected through internal electrodes, and form a loop with a pair of terminal electrodes connected to the same internal electrode unit. The auxiliary terminal electrode can be used as a ground connection terminal.

[0094] The manufacturing method of the multilayer chip varistor of this embodiment includes:

[0095] (1) Configure the slurry: the same as in Example 1

[0096] (2) Lamination: the manufacturing method is the same as that of Embodiment 1, the only difference lies in the design of the internal electrode pattern structure.

[0097] (3)-(8) The manufacturing method is the same as the first embodiment, the only difference is that an ...

Embodiment 3

[0099] Such as Figure 8-12 As shown, the difference between the multilayer chip varistor of this embodiment and the multilayer chip varistor of Embodiment 2 is that: the multilayer chip varistor of this embodiment also includes multiple The resistance layer 6 on the upper substrate and / or the lower substrate, the two ends of each resistance layer 6 are respectively connected to a pair of terminal electrodes 2 connected to the same internal electrode unit 7; and the upper surface of the resistance layer has a layer of organic Material protective layer or inorganic material protective layer 5 cover. The resistance layer 6 is used to form an R-C loop in the varistor, so that the multilayer chip varistor of this embodiment has the function of anti-electromagnetic interference, and the protective layer 5 has insulation and waterproof functions, and is used to protect the resistance layer. Its material Preferable polymer materials, such as epoxy resin, phenolic resin and other mat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com