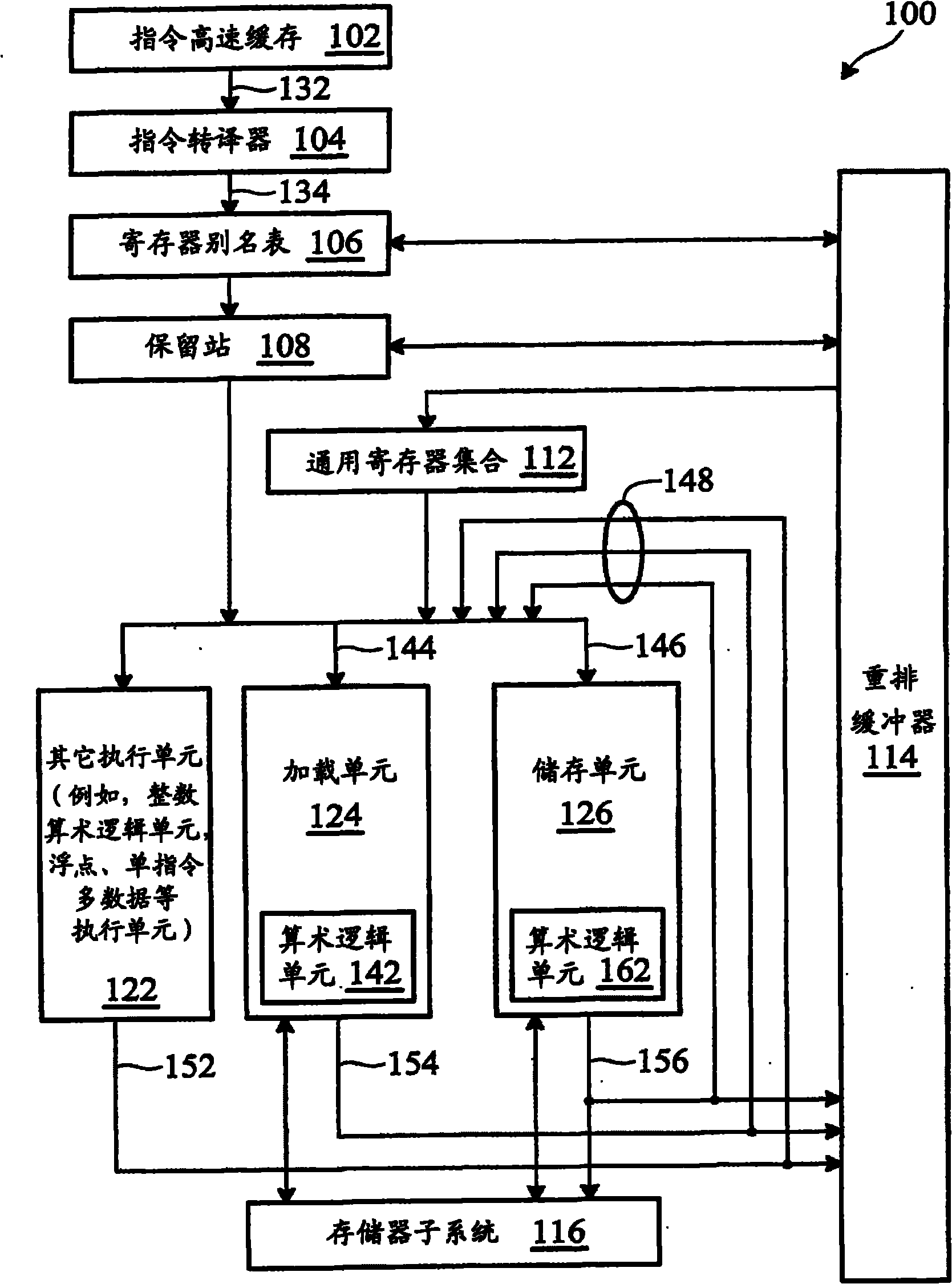

Microprocessor with alu integrated into load unit

A microprocessor and instruction processing technology, applied in the direction of concurrent instruction execution, machine execution device, etc., can solve the problems of consuming a lot of time and time consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

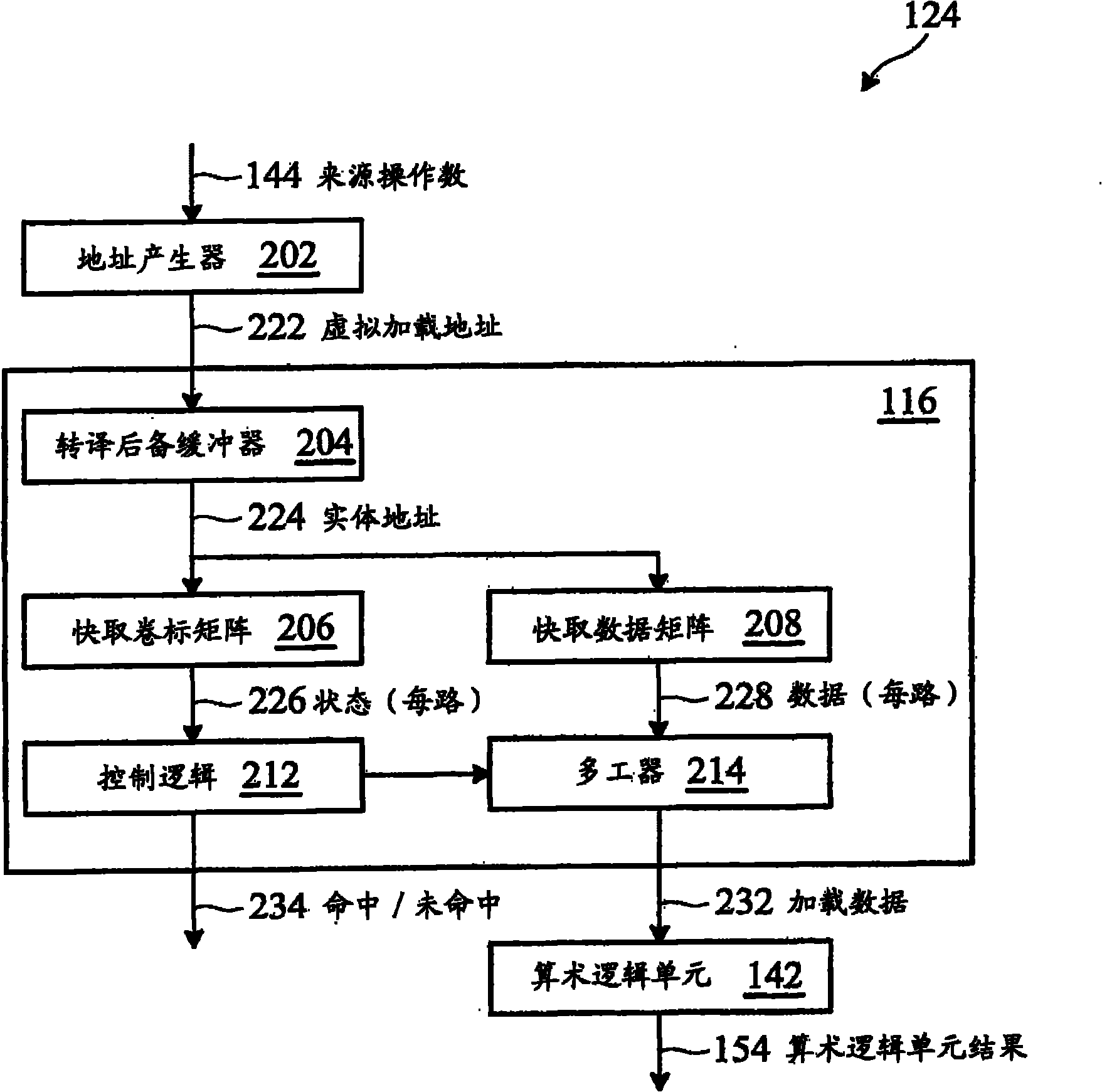

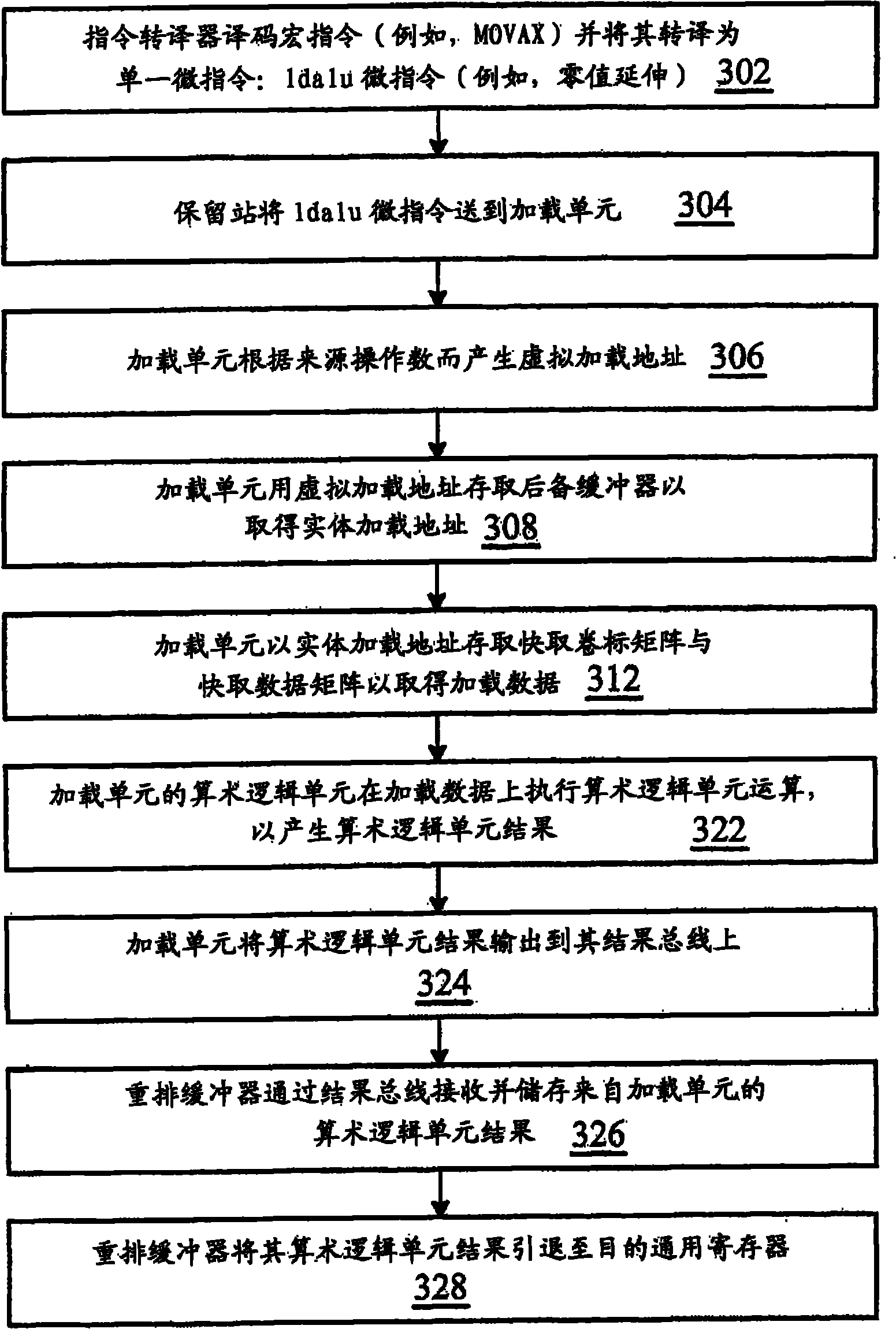

[0053]The inventors of the present invention have found that in the design of a pipeline flow loading unit, a part of frequency cycles may not be used in the last stage, that is to say, the delay time generated by the circuit in the last stage of the loading unit is only A fraction of the frequency cycle time. Therefore, the present invention advantageously integrates an arithmetic logic unit into the last stage of the load unit in an embodiment, so that the load unit can first load the load data extracted from the memory into the destination register. Perform arithmetic logic operations. Through this advantageous design, the time required for transferring the loaded data to another ALU to execute the ALU can be saved. The microprocessor of the present invention uses a load / store microprocessor architecture that implements the non-load / store x86 architecture of the processor (or the macroarchitecture of the processor). The instruction translator generates a special type of l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com