Front-end sampling hold and margin amplification circuit of analog-to-digital converter

An analog-to-digital converter, sample-and-hold technology, used in analog-to-digital converters, electrical analog memories, instruments, etc., can solve the problems of limited sampling rate, unfavorable accuracy, limited accuracy, etc., to reduce power consumption and improve linearity. , the effect of improving the accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

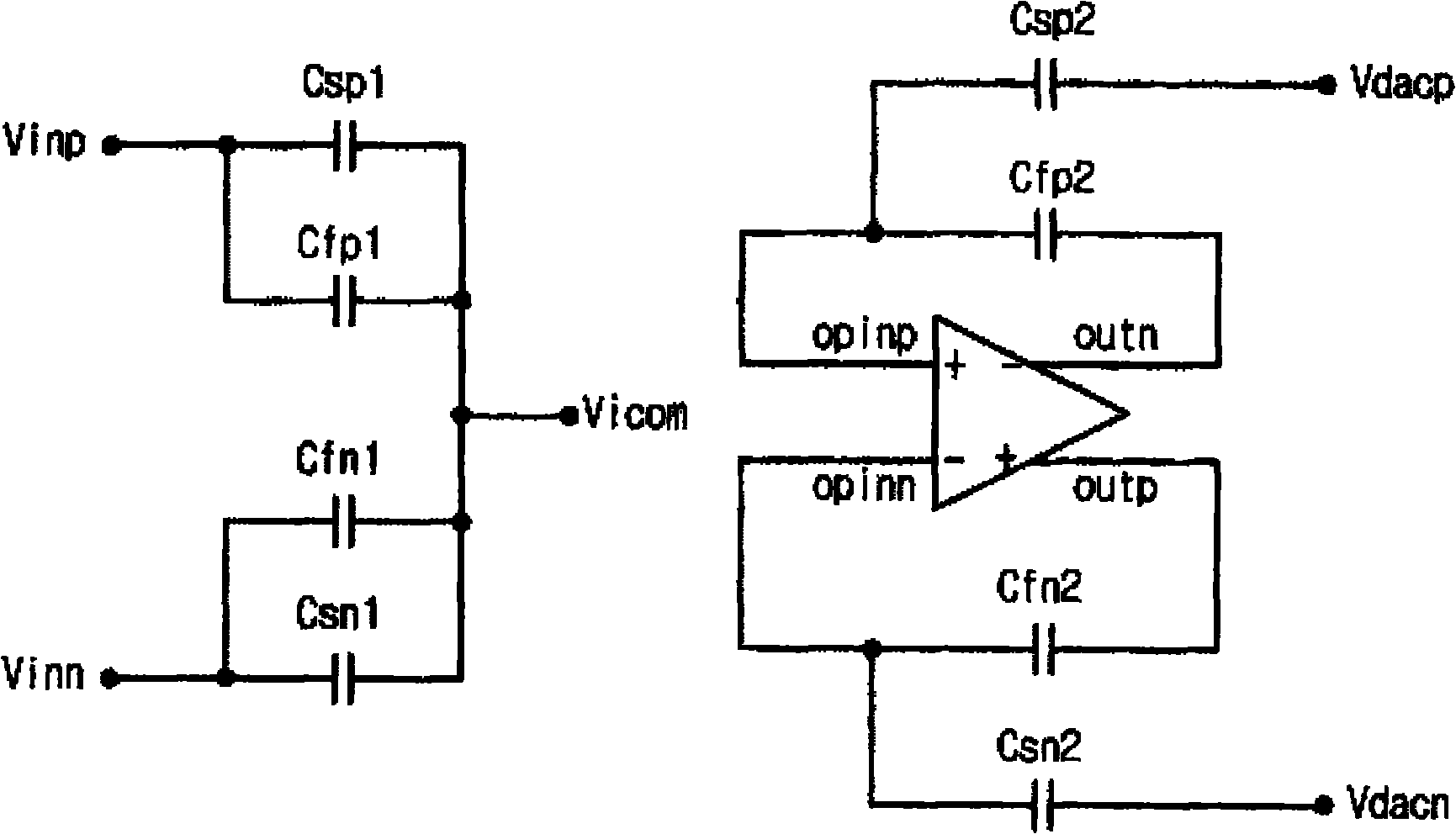

[0027] like figure 1 as shown, figure 1 The present invention provides a schematic structural diagram of a circuit for sample-holding and margin amplification at the front end of a pipelined analog-to-digital converter. The circuit includes an operational amplifier, a first switched capacitor unit, a second switched capacitor unit, and two sampling switches. Wherein, the first switched capacitor unit and the second switched capacitor unit alternate with the operational amplifier and two sampling switches to form a sample-hold and margin amplifier circuit. In the sampling phase, the first switched capacitor unit or the second switched capacitor unit and the two sampling switches sample the current sample, while the second switched capacitor unit or the first switched capacitor unit and the operational amplifier make a margin for the last sampled sample Amplification; in the hold phase, the first switched capacitor unit or the second switched capacitor unit and the operational ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com