Performance counter for microcode instruction execution and counting method

A technology of instruction execution and counting device, which is applied in the field of counting the execution times of microcode instructions, and can solve the problems of microcode difficulty, no function provided, microcode obtaining observation, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

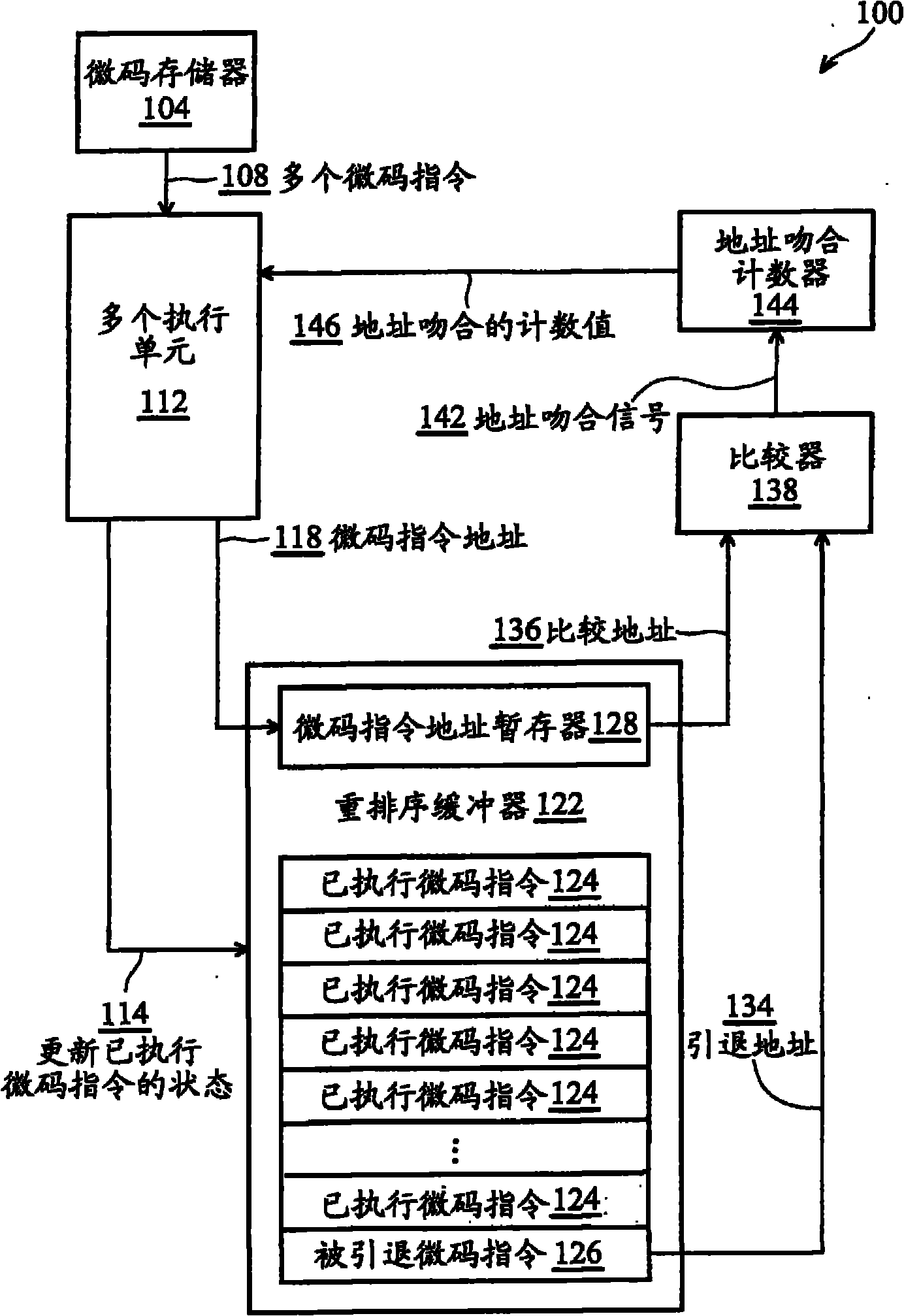

[0032] refer to figure 1 , shows a block diagram of a microprocessor 100 according to the present invention. In response to the microprocessor 100 receiving user program instructions, the microcode memory 104 stores a plurality of microcode instructions 108 provided by it to a plurality of execution units 112. In addition, although not shown in figure 1 Among them, microcode instructions from other sources, such as microcode instructions from an instruction translator or an instruction cache (not shown) of the microprocessor 100, are also provided to the plurality of execution units 112 for execution. In an embodiment of the present invention, the plurality of execution units 112 execute microcode instructions out of order.

[0033] The microprocessor 100 also includes a reorder buffer 122 coupled to the plurality of execution units 112. microcode instruction 108) assigns an item (entry) 124 or 126, and when a plurality of microcode instructions 108 are sent to a plurality o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com