Multi-core timer implementing method and system

A technology of a multi-core system and an implementation method, which is applied in the field of computer multi-core, can solve problems such as the lower half bottom cannot be scheduled in time, the timer processing is not timely, and the timer timeout is not supported, so as to achieve the conditions of improving polling efficiency and deploying Easy to avoid the effect of inaccurate timer

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

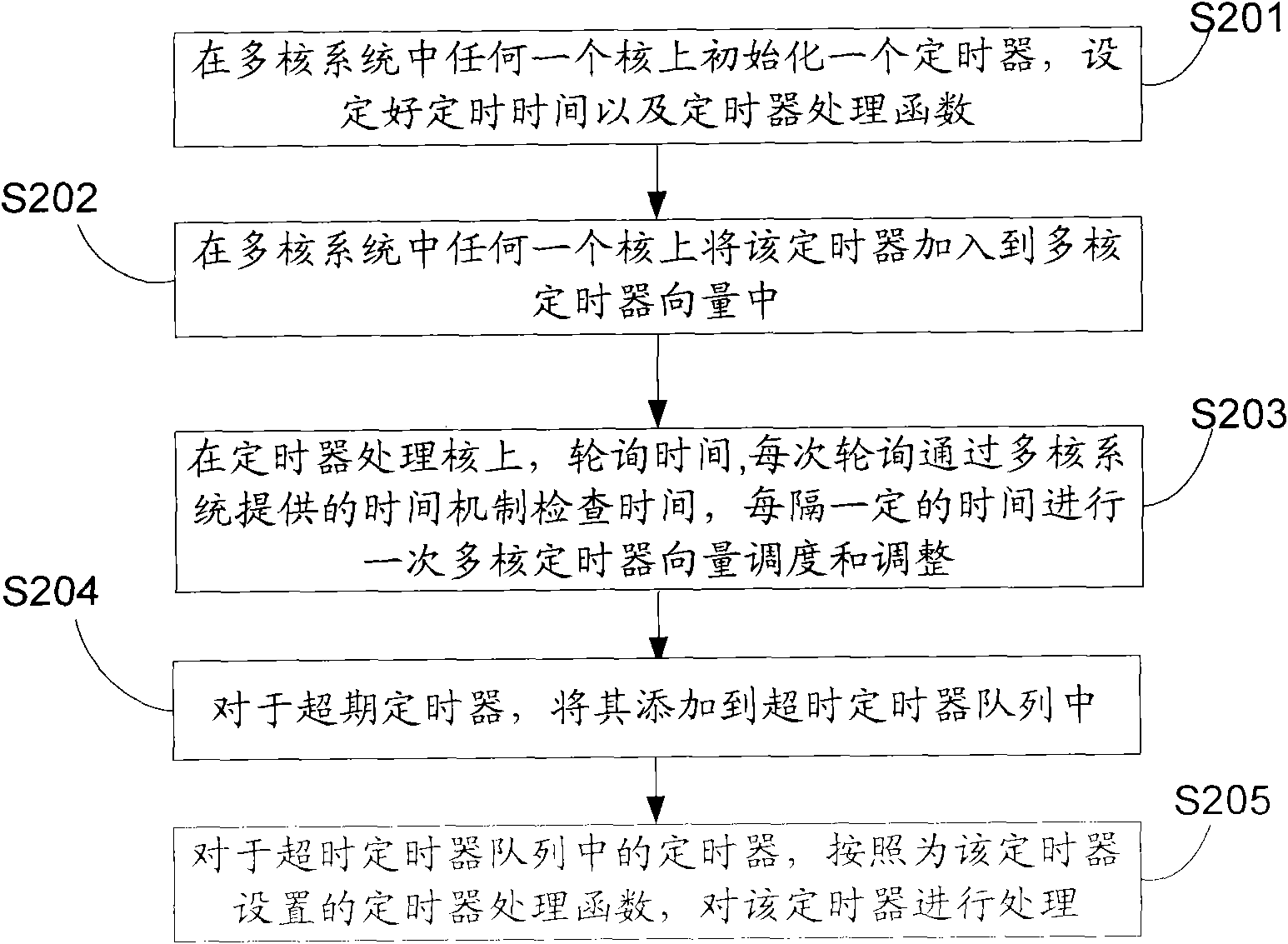

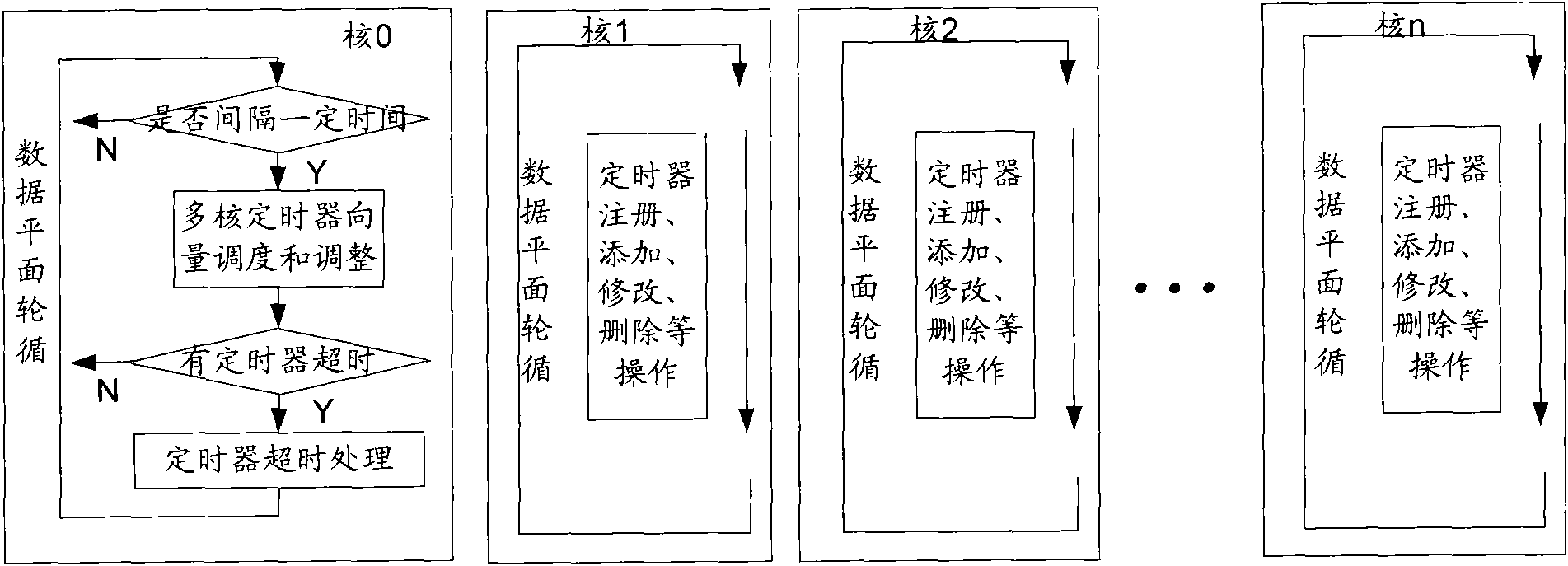

[0041] The present invention provides a multi-core timer implementation scheme for a multi-core system. Unlike the existing Linux timer mechanism, which relies on operating system interrupts and lower half bottoms, the present invention selects a core from multiple cores as the timer processing core, which is determined by The core uses the multi-core system timing function to execute the scheduling and adjustment of the multi-core timer vector, which gets rid of the dependence on the operating system interrupt and the lower half bottom, and reduces the kernel overhead.

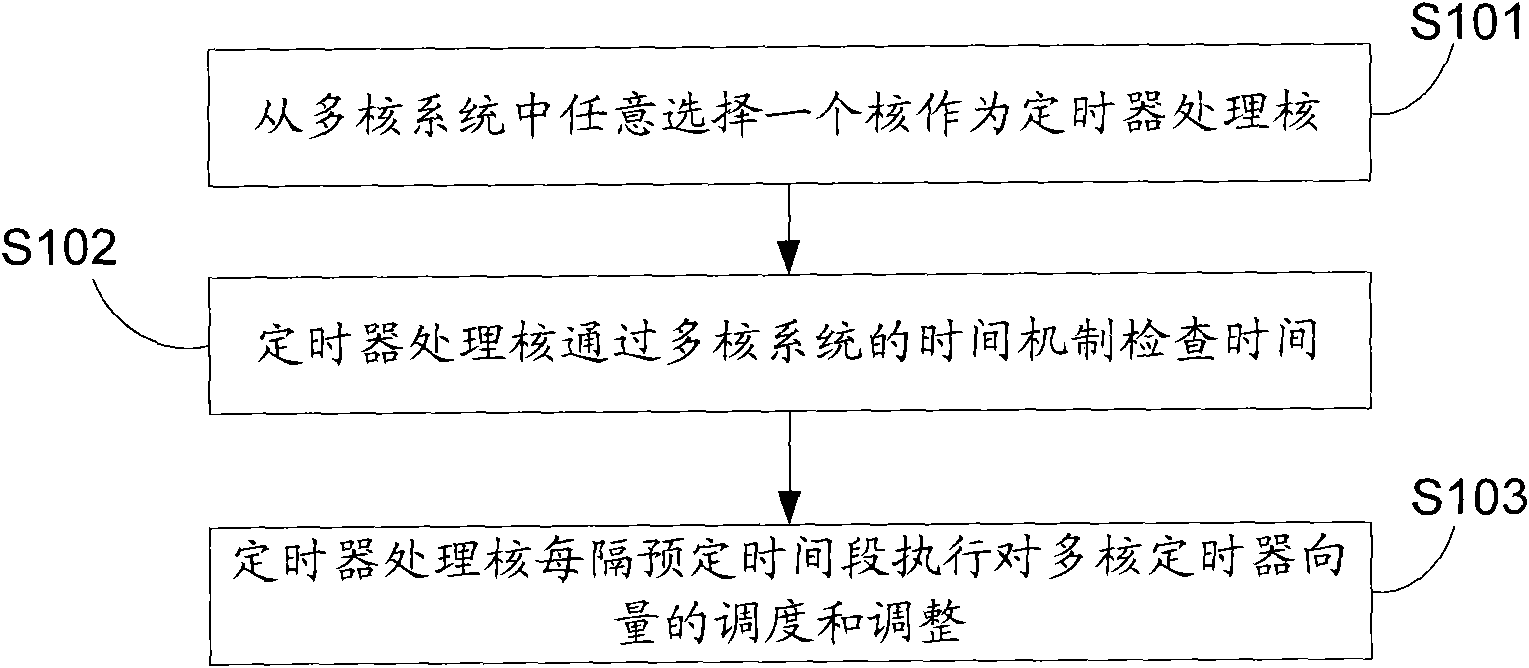

[0042] see figure 1 , which is a flow chart of the multi-core timer implementation method of the present invention, including:

[0043] S101: Randomly select a core from the multi-core system as a timer processing core;

[0044] S102: The timer processing core checks the time through the time mechanism of the multi-core system;

[0045] S103: The timer processing core executes the scheduling and adjustment ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com