Clock domain crossing timing simulation system and method

A cross-clock domain and simulation system technology, applied in the computer field, can solve the problems that the simulation cannot continue to proceed correctly, and the real situation of the unfavorable reaction system can be solved.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

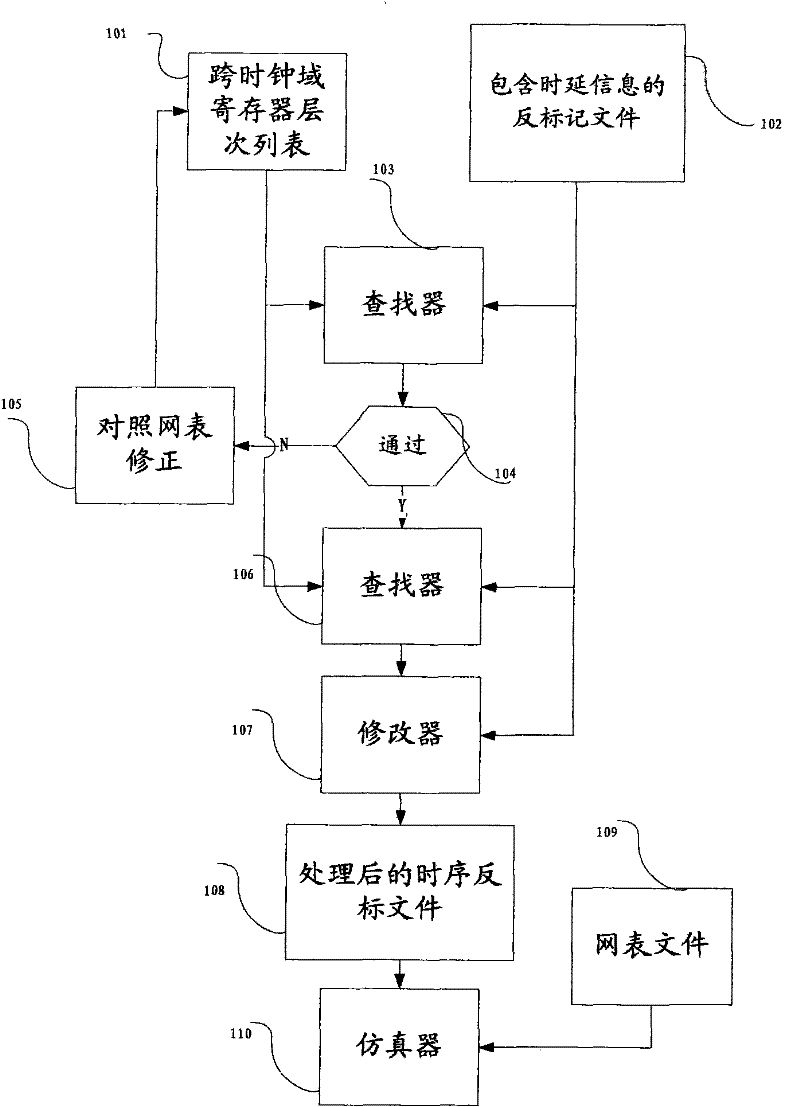

[0029] see figure 1 , The invention discloses a timing simulation system across clock domains, the system includes a finder, a modifier and a simulator.

[0030] 【Finder】

[0031] The finder is used to confirm that all the hierarchical path files of the cross-clock domain registers can be found in the timing back-annotation file, otherwise, the hierarchical path of the corresponding cross-clock domain registers in the cross-clock domain register hierarchical path list is corrected according to the netlist ; Then search for the position of the cross-clock domain register (all cross-clock domain registers in the hierarchical path list) in the timing back-annotation file, and output the position of the cross-clock domain register to the modifier.

[0032] The search process of the finder is: list the register hierarchy path files across clock domains, and the finder searches the clock domain registers in the hierarchical path list in the timing back-annotation file; if not found...

Embodiment 2

[0059] see figure 1 , Figure 4 , this example combines figure 1 The timing simulation system and simulation method across clock domains of the present invention are introduced.

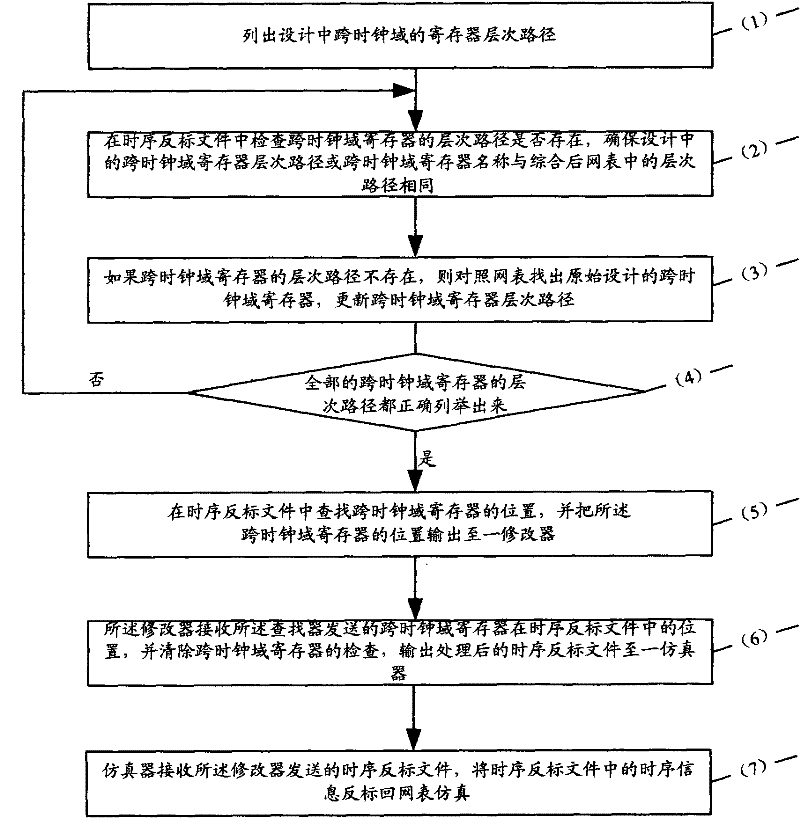

[0060] Such as figure 1 As shown, the input of the finder 103 is the cross-clock domain register hierarchy path list 101 and the timing anti-annotation file 102 containing delay information, and the finder 103 checks whether the cross-clock domain register hierarchy path list 101 exists in the timing anti-annotation file containing timing information. In the marking file 102, if the cross-clock domain register hierarchical path list 101 contains entries that do not exist in the timing reverse marking file 102, it is necessary to correct the corresponding cross-clock domain register in the cross-clock domain register hierarchical path list according to the netlist. Hierarchical path; if the entries in the cross-clock domain register hierarchy path list 101 can be found in the timing anti-annotation...

Embodiment 3

[0065] In this embodiment, there is a netlist including a cross-clock domain design and a corresponding timing anti-annotation file, and timing simulation needs to be performed on the netlist.

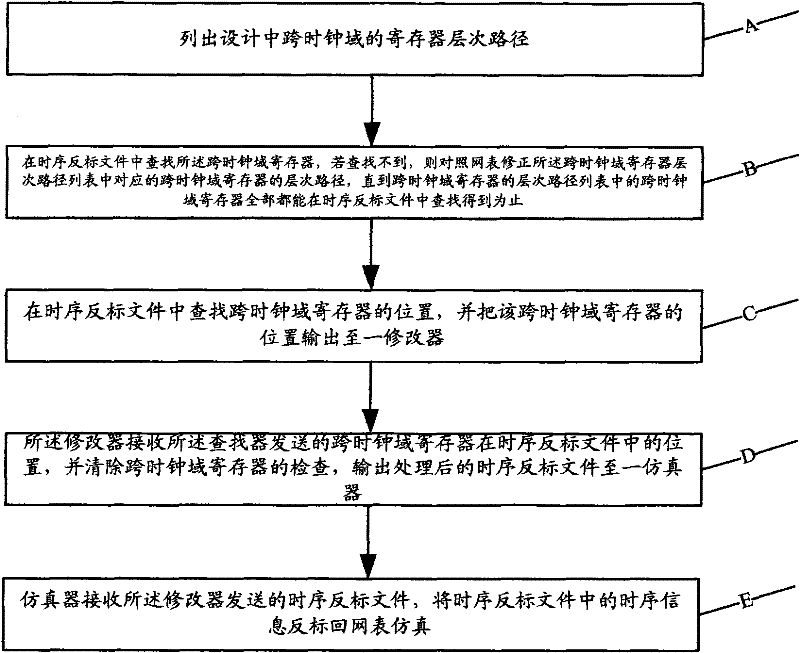

[0066]First point out the cross-clock domain registers in the design, which are given in the form of hierarchical paths, and search for these cross-clock domain registers in the timing back-annotation file. If they cannot be found, correct the hierarchical path list of the cross-clock domain registers according to the netlist The hierarchical path of the corresponding cross-clock domain register in the list, until all the cross-clock domain registers in the hierarchical path list of the cross-clock domain register can be found in the timing back-annotation file; if all the hierarchical paths of the cross-clock domain register can be If it is found in the timing anti-annotation file, the next step is processed on the timing anti-annotation file, and the position of the cross-clock domain...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com