Multi-core processor oriented real-time thread migration method

A technology of multi-core processors and processor cores, which is applied in the direction of multi-programming devices, program startup/switching, etc., can solve problems such as difficult to achieve load balance, and achieve the effect of improving performance and shortening time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

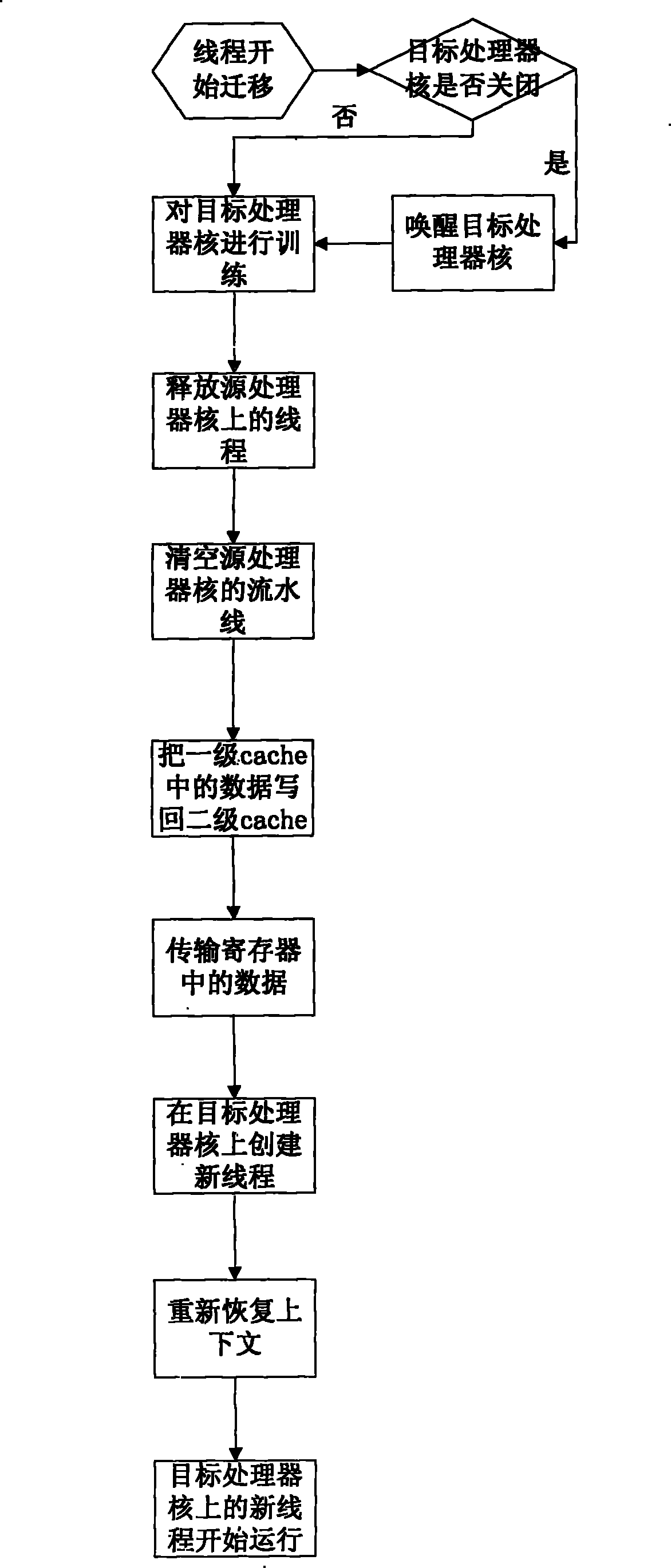

[0024] 1) Thread migration between processor cores, all processor cores have private first-level cache, shared second-level cache and memory:

[0025] In most current multi-core processor architectures, processor cores have a private L1 cache and share L2 cache and memory. All processor cores share memory, so there is no need to transfer code and data in shared memory during thread migration. All processor cores share the second-level cache. When threads migrate, the data in the first-level cache of the source processor core only needs to be written back to the second-level cache instead of being written back to the memory.

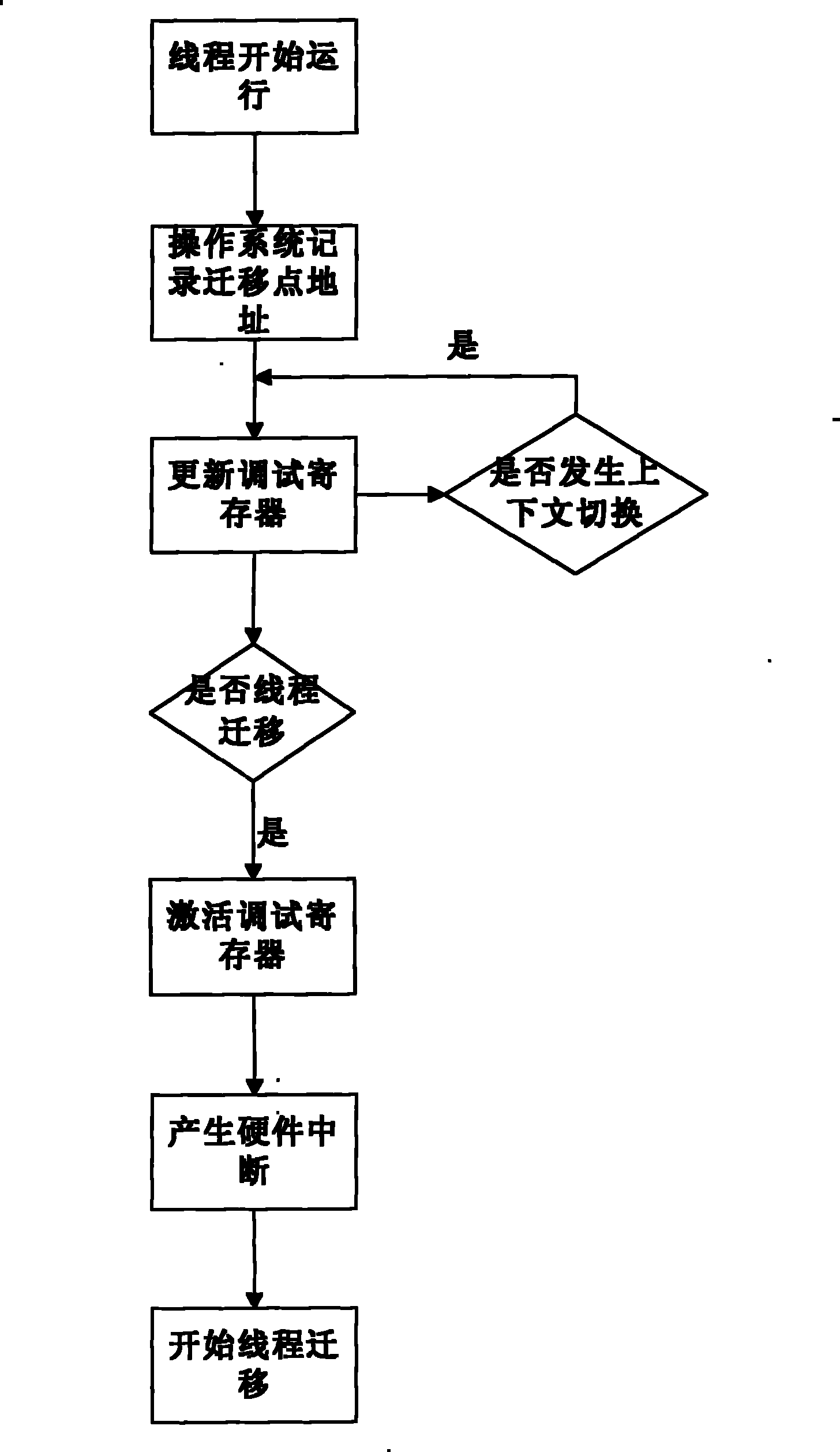

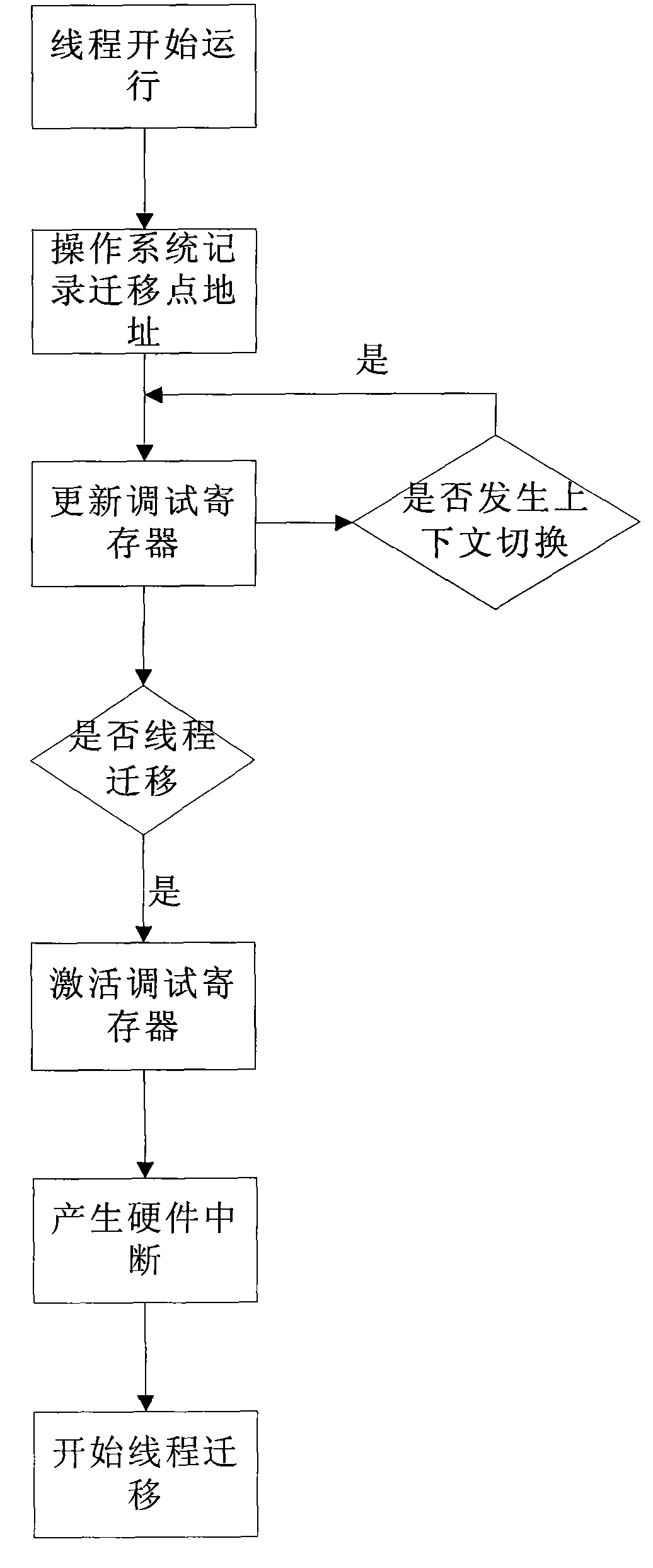

[0026] 2) Thread migration initialization supported by hardware:

[0027] Most modern processors contain a series of debug registers. The PowerPC 405 processor contains four 32-bit instruction address compare registers. A hardware interrupt is generated when the value in the program count register equals the value in the address compare register of an ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com