Parallel implementing method for determinant block interleaving device

A technology of packet interleaving and implementation method, applied in the field of communication, can solve the problems of fixed parallelism, impracticality, and a large number of register resources, and achieve the effect of improving the data processing rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example

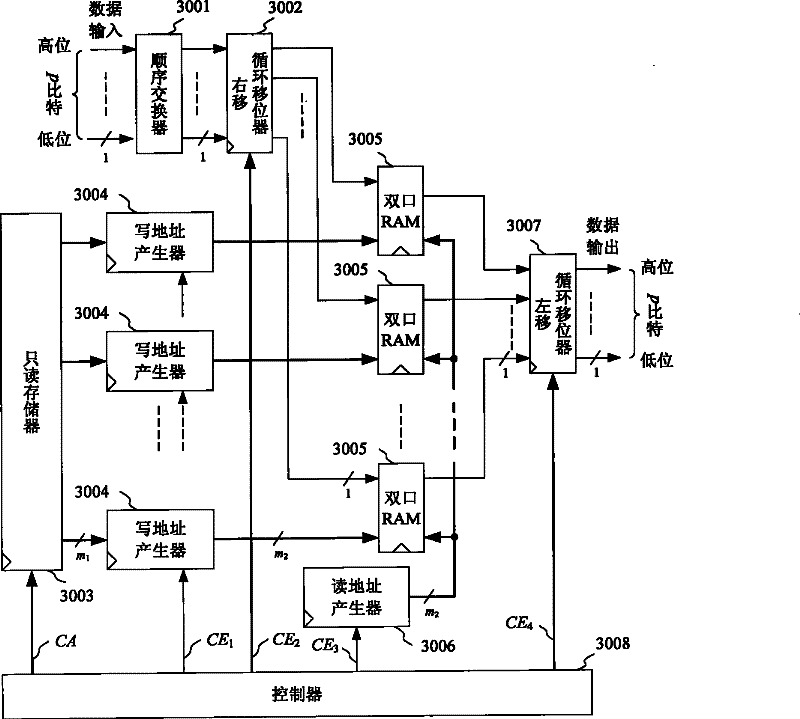

[0068] Assume: interleaving depth d=6, interleaving width n=12, parallelism p=4, according to the formula n=w×p, then w=3.

[0069] Let a frame of 72 bits of data be x 0 , x 1 ,...,x 71 .

[0070] Take i equal to 0, 1, 2, 3 respectively, calculate the Indx values according to formula (1) to be (0, 6, 12, 18) respectively, and calculate the Shuf values according to formula (2) to be (0, 2, 1 , 3).

[0071] For 4-bit data (x 0 , x 1 , x 2 , x 3 ), the serial number k is equal to 0, and the SR value is calculated according to formula (3) to be 0. Therefore, the 4-bit data after sequence exchange and 0 times of cyclic shift to the right is (x 0 , x 2 , x 1 , x 3 ), the sequence exchange and right-shift cyclic shift diagram of this 4-bit data is as follows Figure 8 shown in .

[0072] Another example for 4-bit data (x 36 , x 37 , x 38 , x 39 ), the sequence number k is equal to 9, and the SR value is calculated according to formula (3) to be 3, therefore, the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com