Metal gate mosfet by full semiconductor metal alloy conversion

一种金属合金、半导体的技术,应用在MOSFET器件的结构领域,能够解决很难集成nFET和pFET器件等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

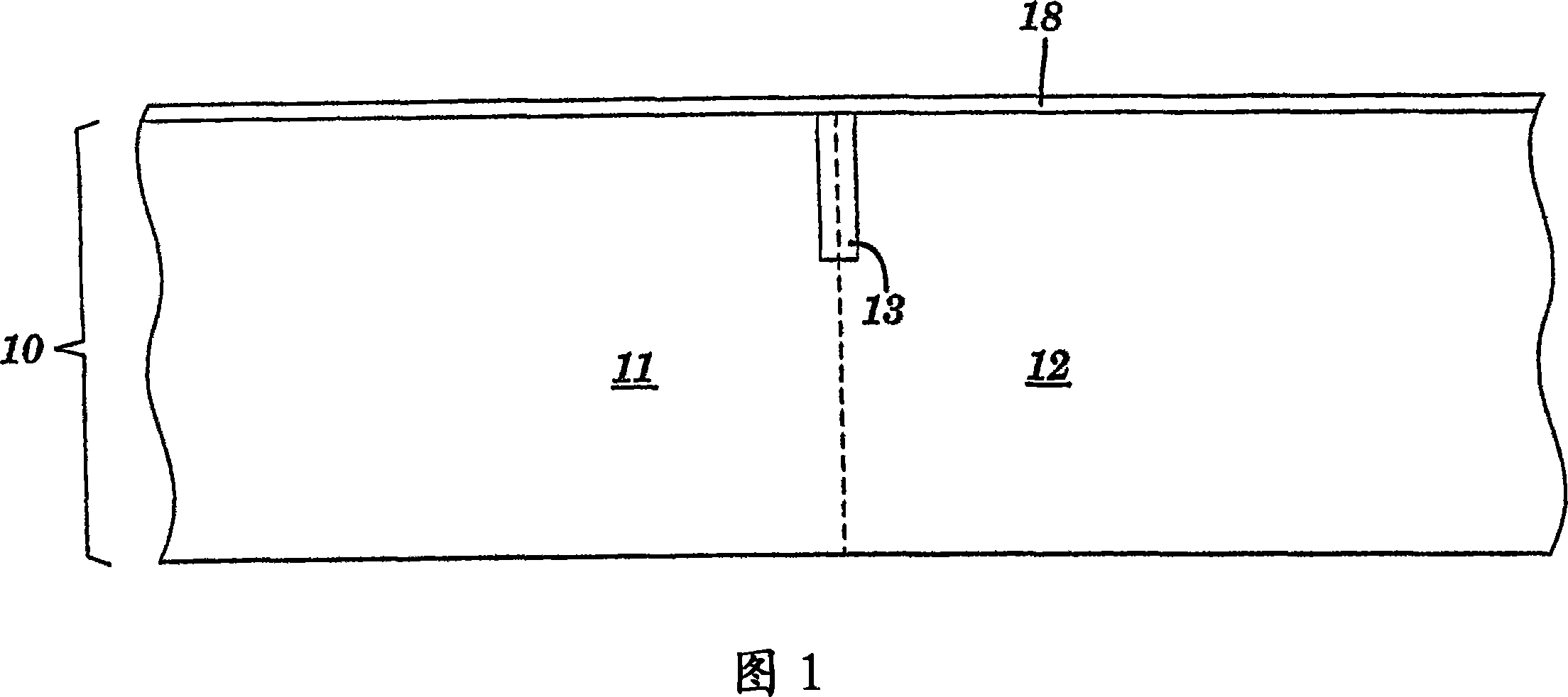

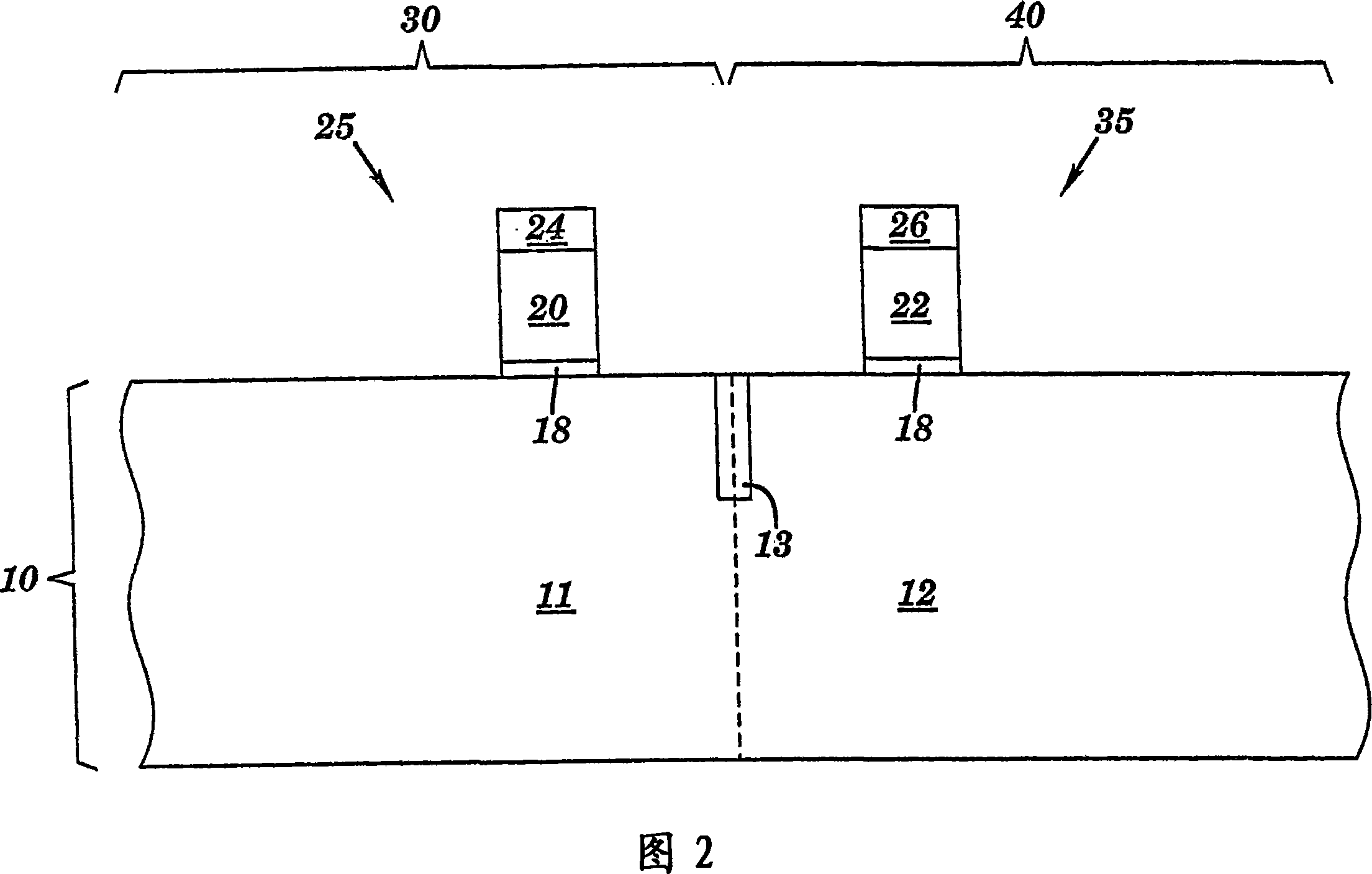

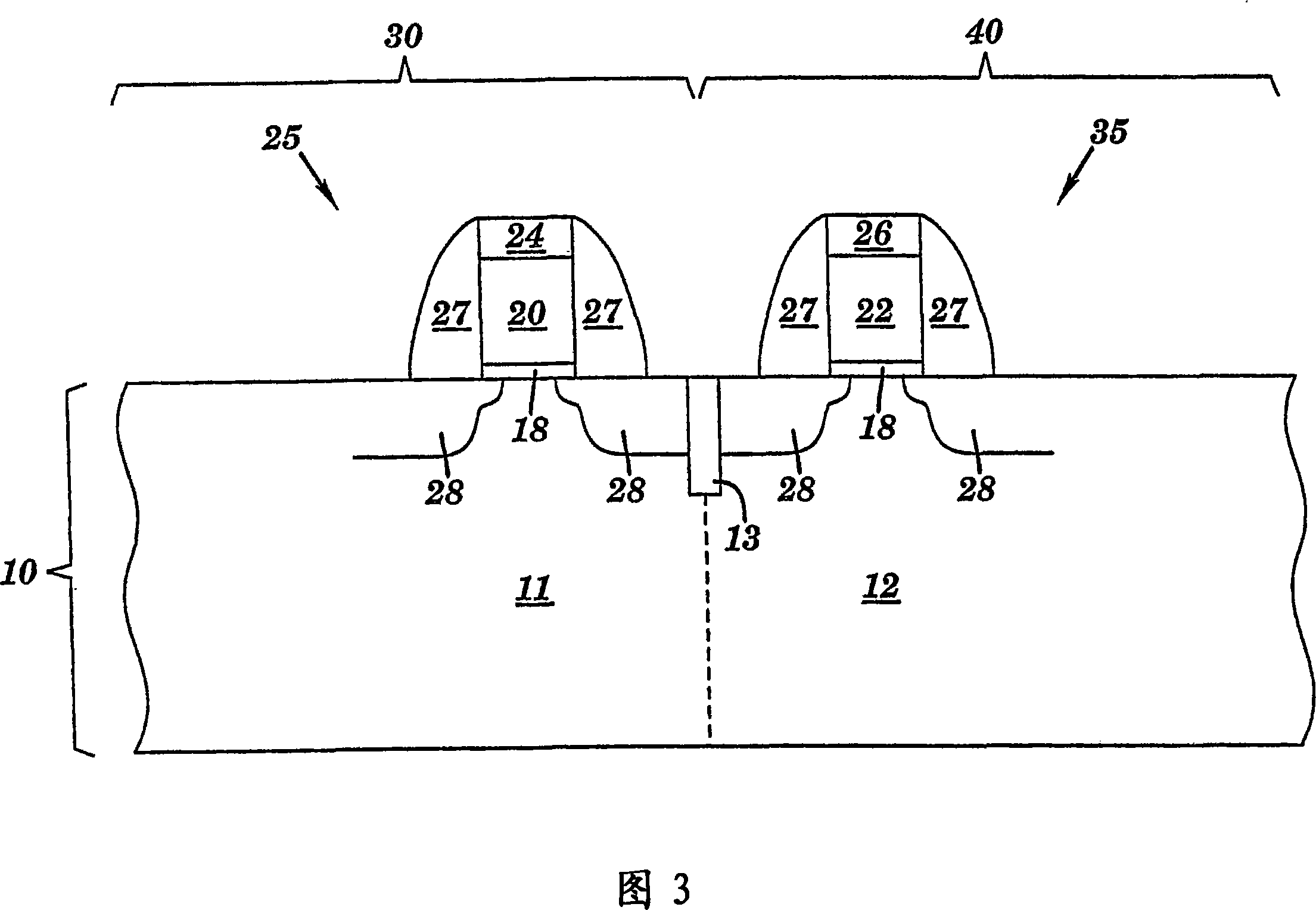

[0017] The present invention will now be described in detail with reference to the drawings accompanying this application, in which the present invention provides a method for combining a MOSFET device of a first type (e.g., nFET) having a fully silicided gate electrode with a MOSFET device having a partially silicided gate electrode. Structures and methods for integrating MOSFET devices of a second type (eg, pFET).

[0018] In accordance with the present invention, a process flow is provided wherein a first type of MOSFET device includes a fully silicided gate electrode, and a second type of MOSFET device has a partially silicided electrode such that both devices have a similar standard polysilicon gate electrode approach. threshold voltage. The techniques described in this disclosure can be applied to densely packed circuits with gate gaps of less than about 200 nm. In the exemplary embodiments described hereinafter, nFETs are implemented with fully silicided gate electrode...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com