Multi-order non-volatility memory and manufacturing method and operation method therefor

A non-volatile, method-of-operation technology, which is applied in static memory, read-only memory, semiconductor/solid-state device manufacturing, etc., can solve the problems of taking a long time and the distribution range of the initial voltage is small, so as to improve the erasing operation speed , save manufacturing cost, increase the effect of process margin

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

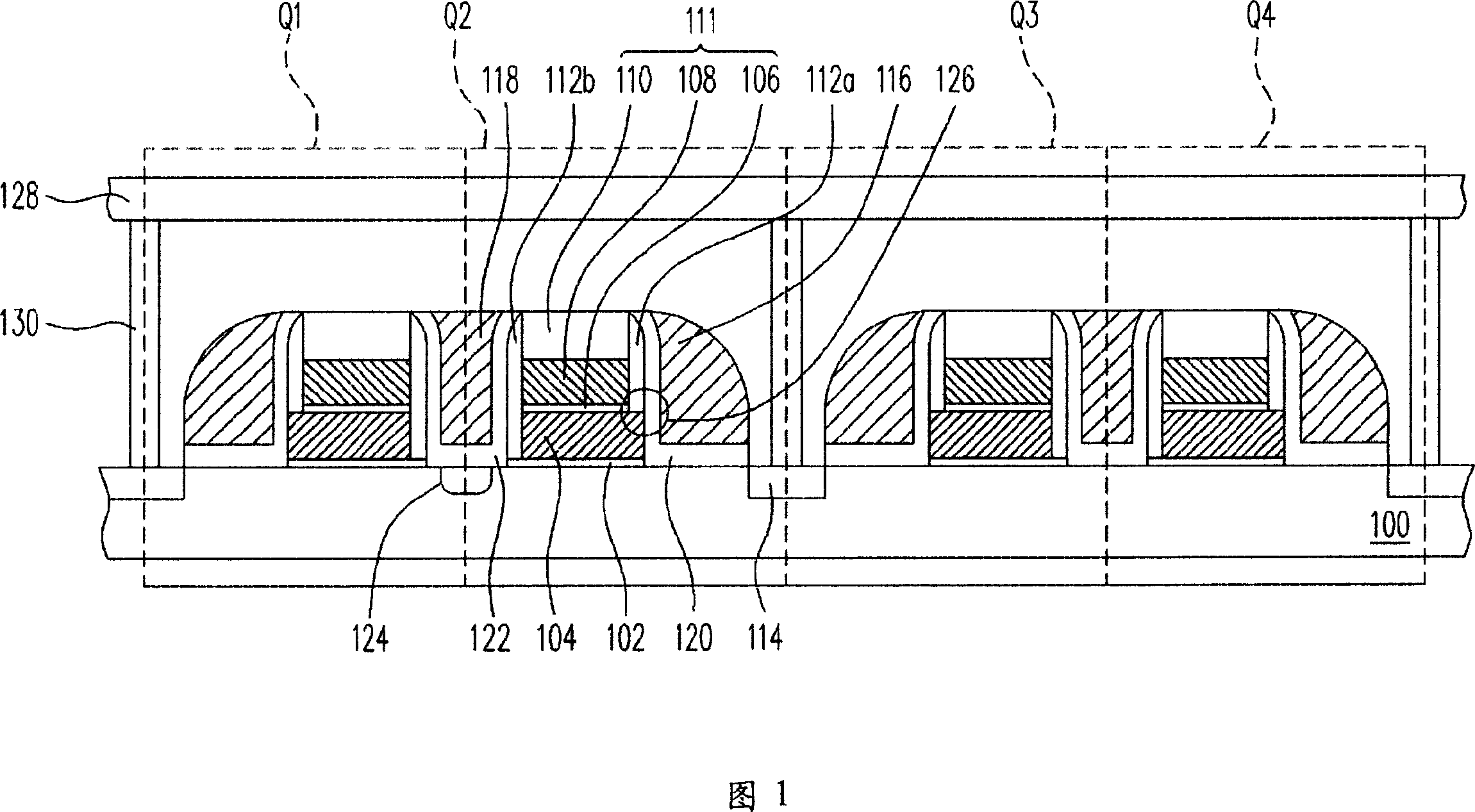

[0099] FIG. 1 is a cross-sectional view showing the structure of a non-volatile memory according to an embodiment of the present invention.

[0100] Referring to FIG. 1 , the multi-level non-volatile memory proposed by the present invention is, for example, composed of a plurality of memory cells Q1 , Q2 , Q3 , and Q4 disposed on a substrate 100 . Each memory cell Q1, Q2, Q3, Q4 includes a tunneling dielectric layer 102, a charge storage layer 104, an intergate dielectric layer 106, a control gate 108, a top cover layer 110, spacers 112a, 112b, and a doped region 114 , select gate 116 , auxiliary gate 118 and dielectric layers 120 , 122 . The inter-gate dielectric layer 106 , the control gate 108 , and the top cap layer 110 form a stack layer 111 .

[0101] The control gate 108 is, for example, disposed on the substrate 100 . The material of the control gate 108 is, for example, doped polysilicon.

[0102] The charge storage layer 104 is, for example, disposed between the c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com