Multilayer printed wiring board

A multi-layer printing and circuit board technology, applied in the direction of printed circuit, printed circuit, printed circuit manufacturing, etc., can solve the problems of peeling, poor ductility, easy cracking of electroless plating film, etc., to improve the integration rate and connection reliability. reduced effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment

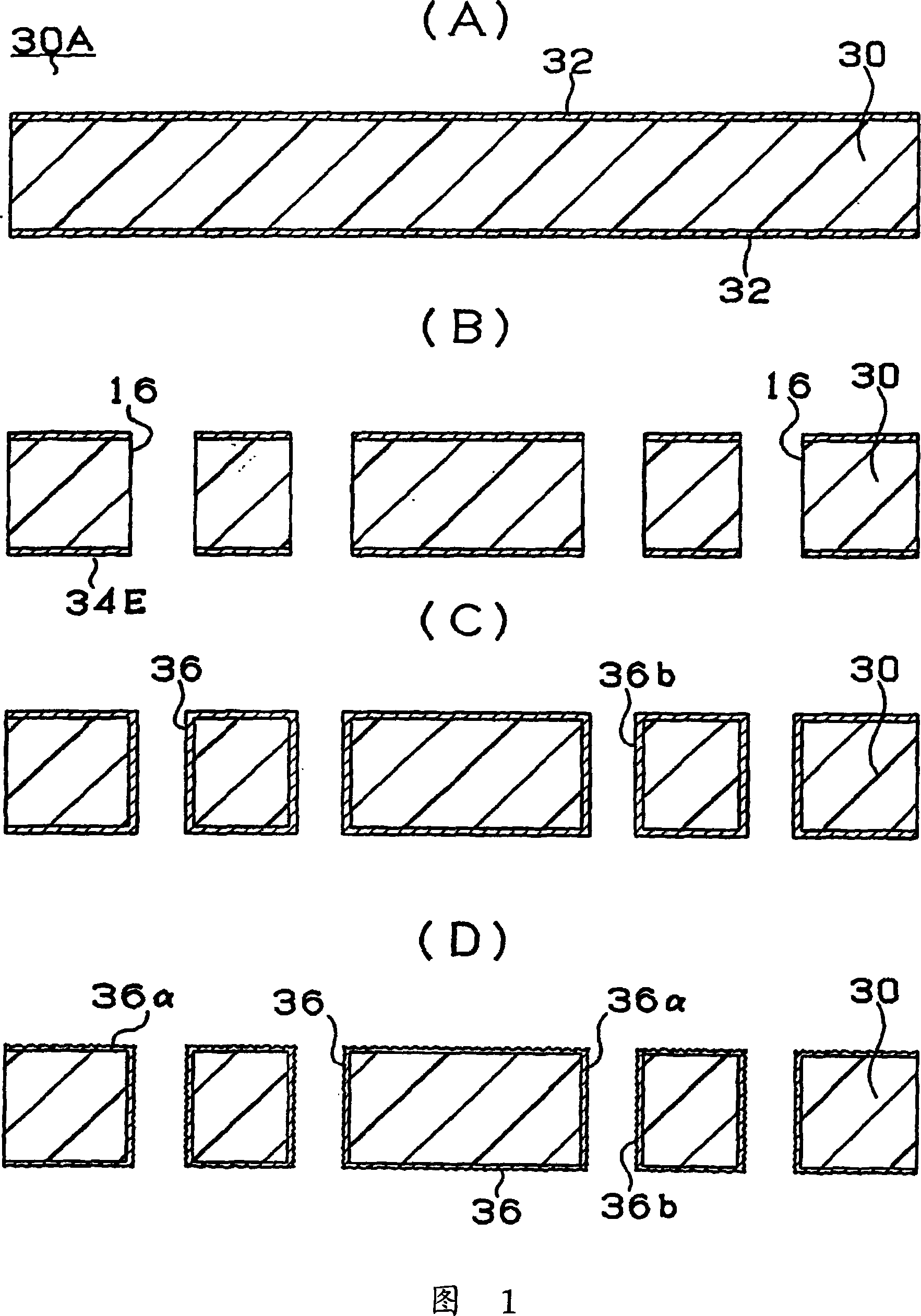

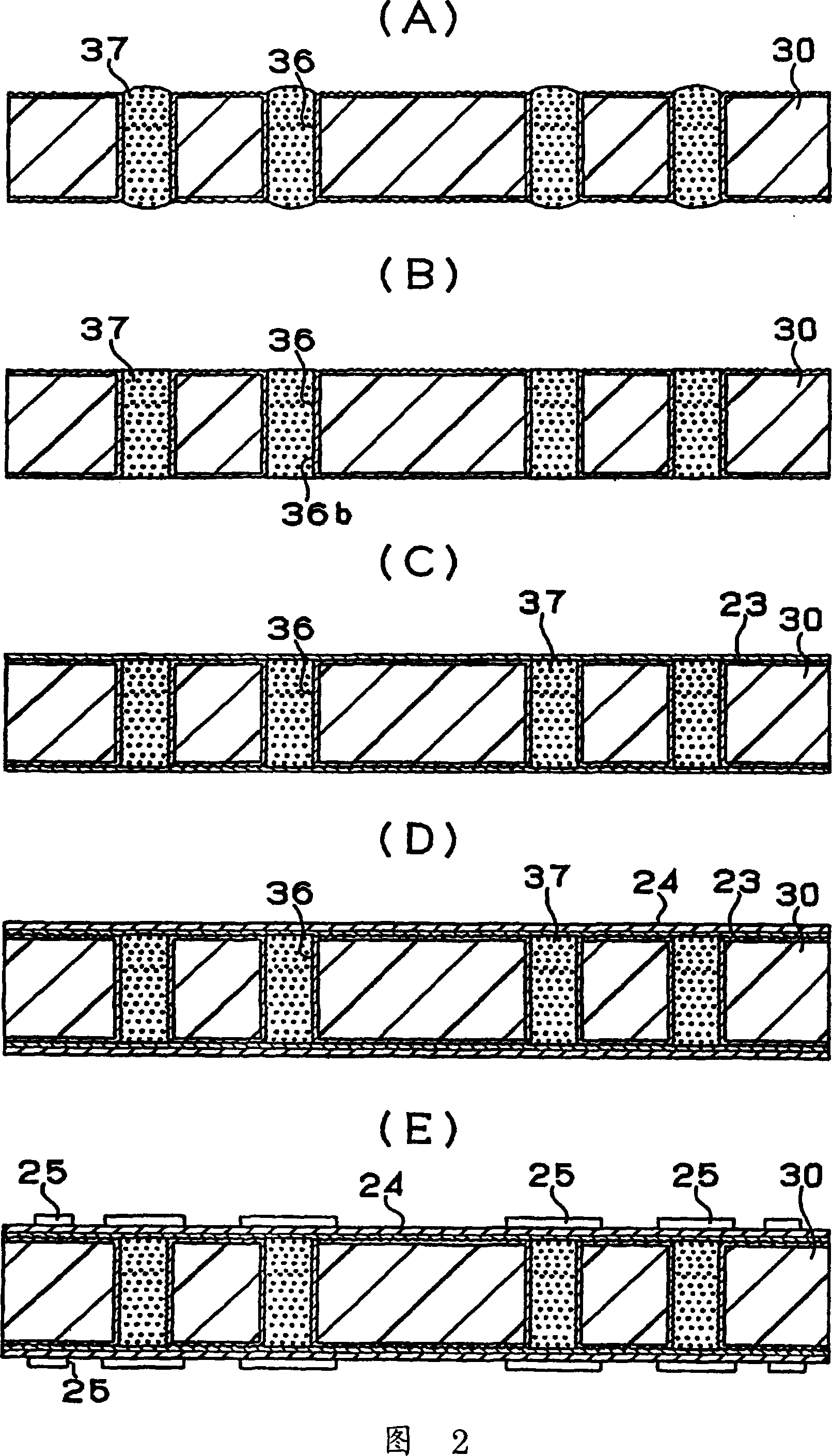

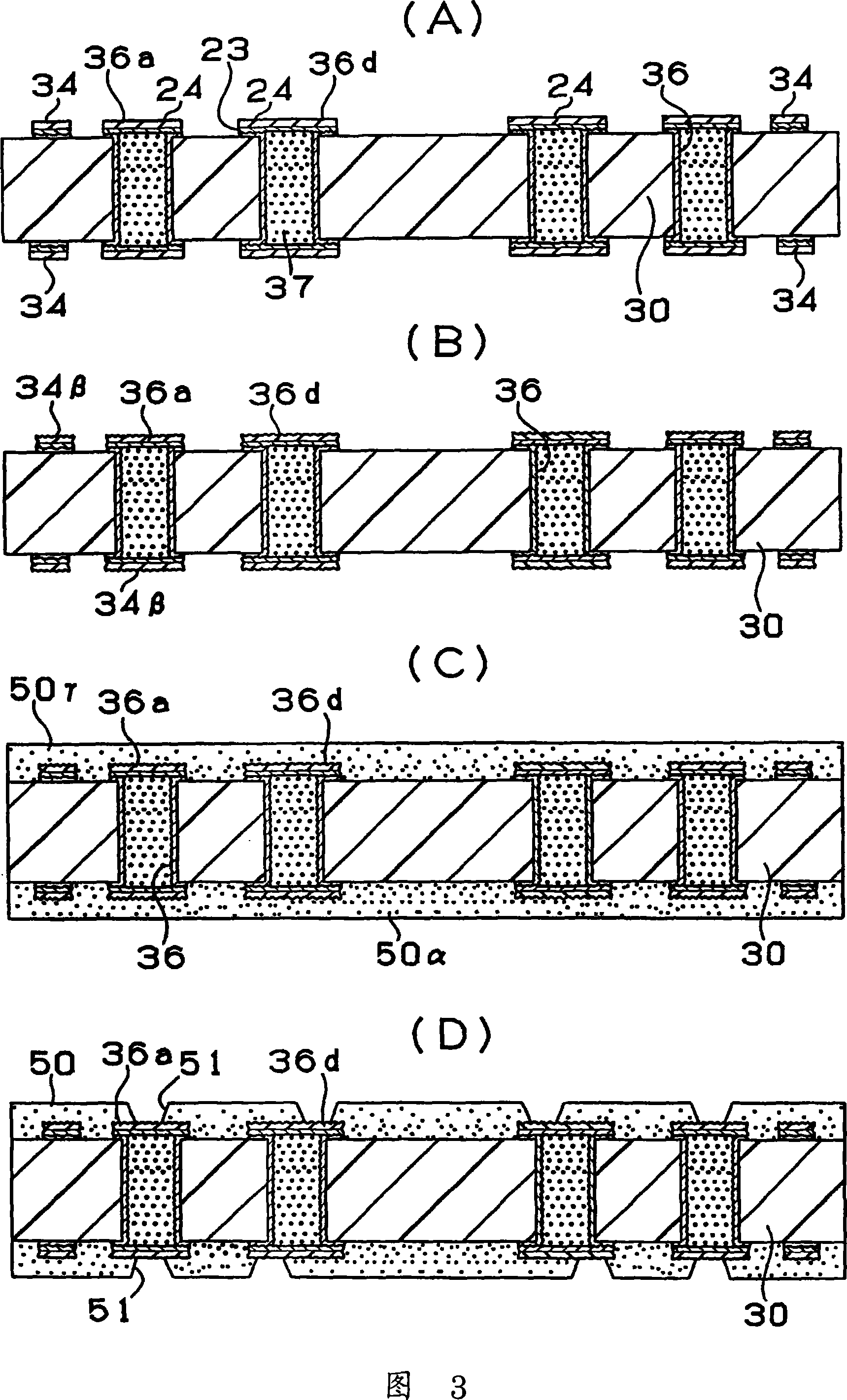

[0029] First, the structure of a multilayer printed wiring board 10 according to a first embodiment of the present invention will be described with reference to FIGS. 1 to 8 . FIG. 7 shows a cross-sectional view of the multilayer printed wiring board 10, and FIG. 8 shows a process of mounting an IC chip 90 on the multilayer printed wiring board 10 shown in FIG. state. As shown in FIG. 7 , in the multilayer printed wiring board 10 , conductor loops 34 are formed on the surface of the core substrate 30 . The front and back surfaces of the core substrate 30 are connected by through holes 36 . The through hole 36 is composed of capping plating layers 36a, 36d constituting the through hole land, and a side wall conductor layer 36b, and the inside of the side wall conductor layer 36b is filled with a resin filling material 37. It is also possible to fill only copper without using a resin filler. The interlaminar resin insulating layer 50 and the interlaminar resin insulating laye...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Radius | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com