Manufacturing method for multi-layer high-density interconnected printed circuit board

A high-density interconnection, printed circuit board technology, applied in the direction of multi-layer circuit manufacturing, printed circuit components, electrical connection printed components, etc. Complexity and other issues, to achieve the effect of reducing the production cycle, reducing the size of the board, and simplifying the process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

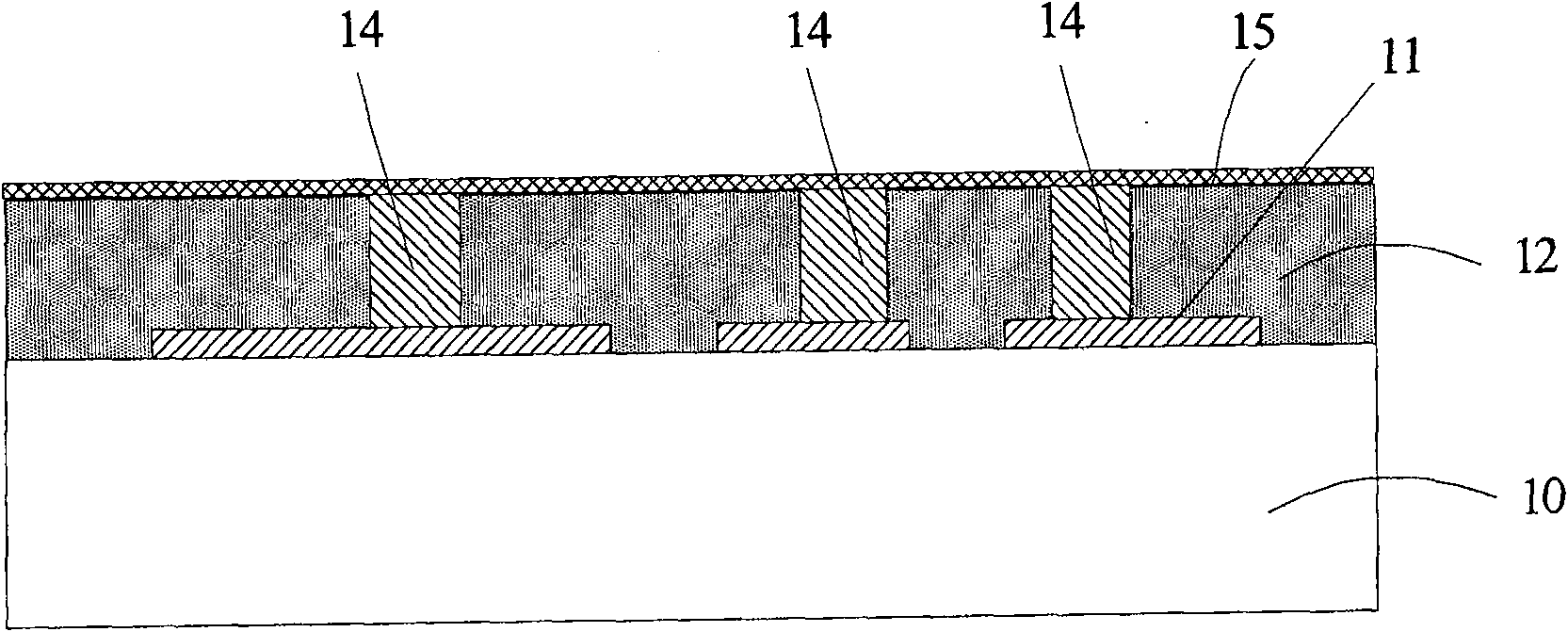

[0027] This embodiment provides a method for manufacturing a multilayer high-density interconnection printed circuit board. Refer to the attached Figure 4 In the process flow diagram shown, in step S300, a substrate is provided, and one or two circuit planes of the substrate have a first wiring layer, and the first wiring layer is formed on the first wiring layer for interconnection between the wiring layers. a first conductive bump,

[0028] Step S301, 1) forming an insulating medium layer covering the first wiring layer and the first conductive bump on the substrate, and performing planarization treatment to expose the end surface of the first conductive bump;

[0029] Step S302, 2) forming a conductive layer on the insulating dielectric layer;

[0030] Step S303, 3) forming a first insulating layer on the conductive layer and forming a second wiring layer pattern on the first insulating layer;

[0031] Step S304, 4) depositing a conductive material on the conductive laye...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com