Detecting structure for simultaneously detecting hot carriers of multiple metal-oxide-semiconductor device

A hot carrier and test structure technology, applied in semiconductor/solid-state device testing/measurement, semiconductor devices, electrical components, etc., can solve problems such as gate oxide layer damage and charge accumulation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

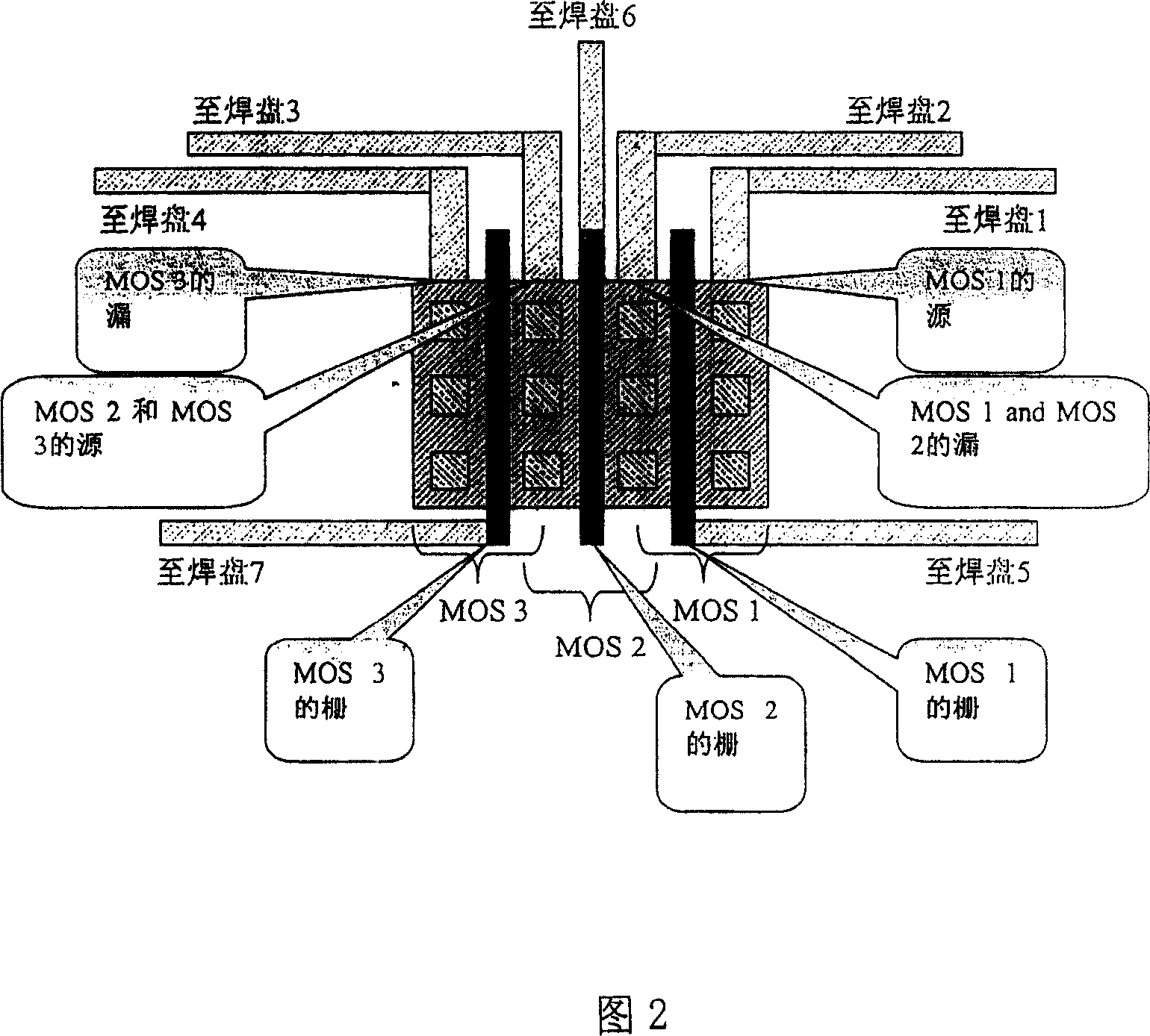

[0019] Referring to accompanying drawing 1 and accompanying drawing 2 below, describe the present invention in detail.

[0020] FIG. 1 is a test structure of an existing MOS device. In the test structure of the MOS device shown in FIG. 1 , there is a polysilicon gate, two sides of the polysilicon gate have a source region and a drain region, and the other side of the source region and the drain region has a drain region and a source region. The polysilicon gate and its side source and drain regions constitute a MOS device unit, and the polysilicon gate and its side source and drain regions are connected to respective pads through metal wires to form a test structure of the MOS device. The dummy polysilicon gate and the area other than the dummy polysilicon gate are not connected to the pad separately, and the dummy polysilicon gate only plays a role in preventing the microscopic effect and etching speed from affecting the length of the polysilicon gate during the etching proce...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com