Transmission using multiple physical interface

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

example pci topology

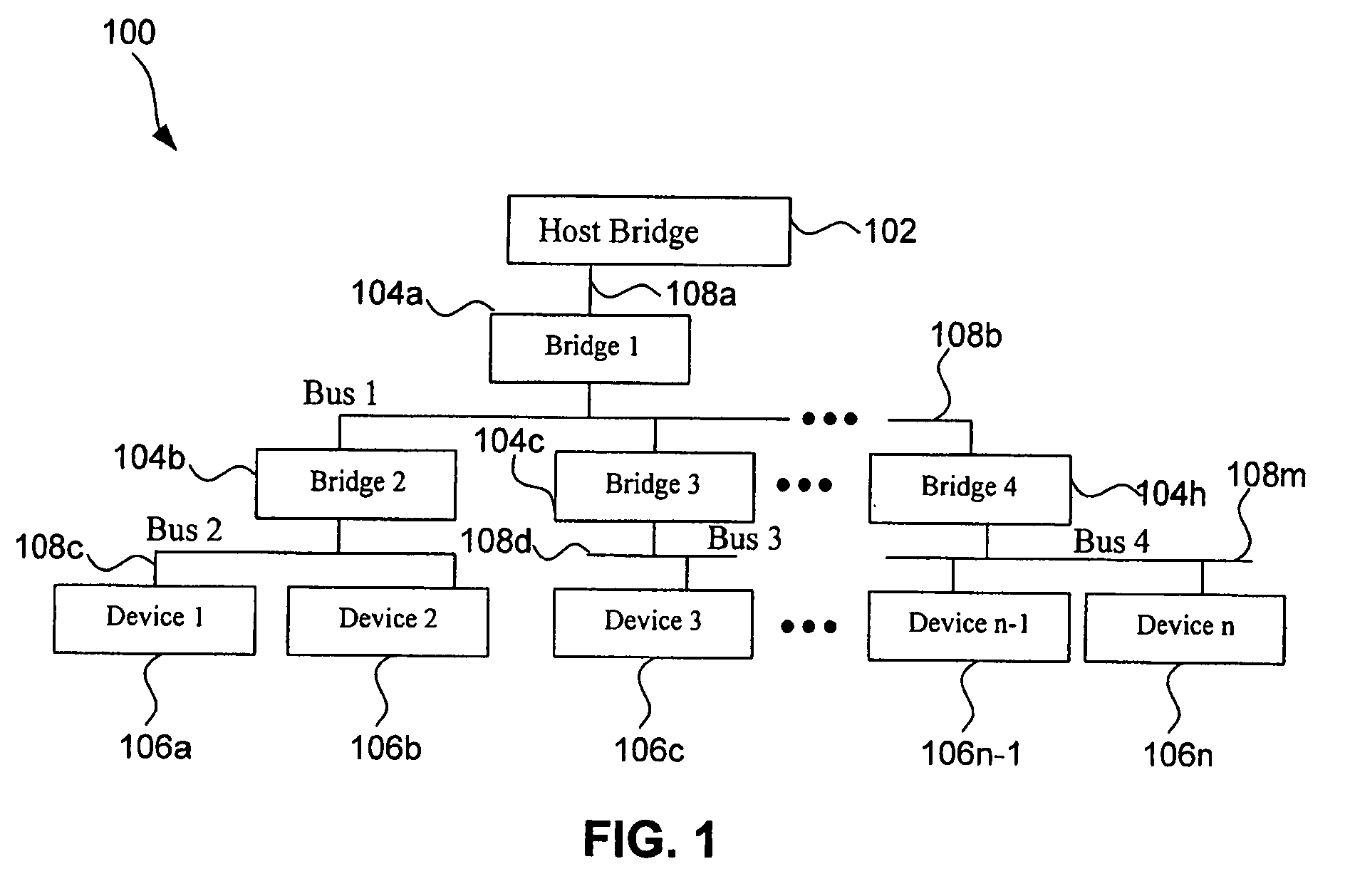

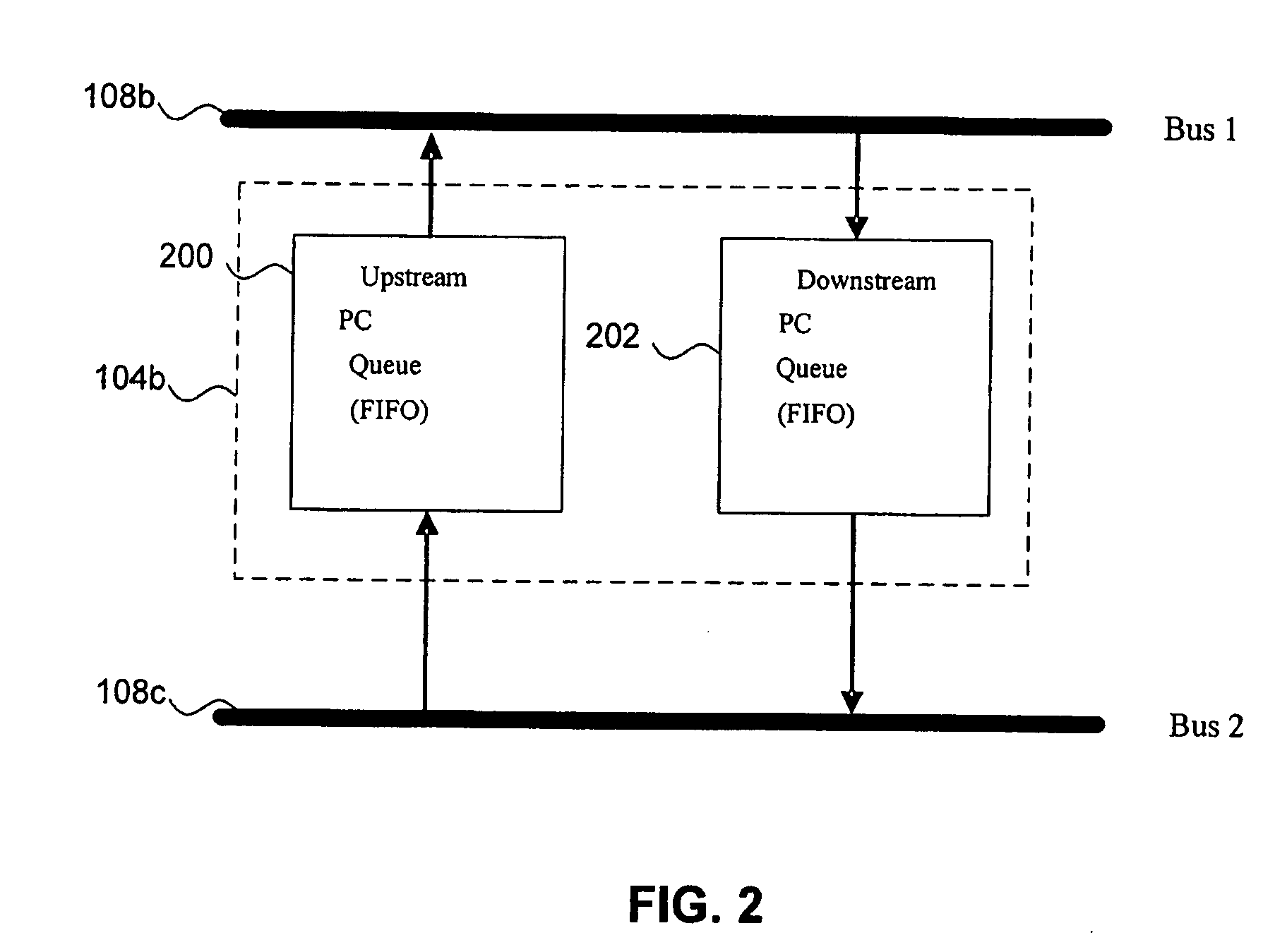

[0028]FIG. 1 illustrates system 100 in a PCI tree topology. System 100 comprises a host bridge 102, bridges 104a-h and devices 106a-n connected by buses 108a-m. Host bridge 102, bridges 104a-h and devices 106a-n may be one or more of network cards, network processors and System on Chips (SOC). Host bridge 102 defines the root of system 100. Bridges 104a-h form a hierarchical network connected by buses 108a-m. Each bridge 104 is associated with a range of device addresses and is enabled to route data to a device 106 that has an address in that range of addresses. Devices 106a-n form “leaves” of the hierarchical bus network.

[0029]If the underlying transmission protocol in system 100 is, for example, a PCI protocol or another protocol that requires strictly ordered transmission, then there is a long latency for communication between devices 104. For example, as shown in FIG. 1, for device 106a to send data to device 106n-1 using a PCI model, data is pushed up to bridge 104b followed by...

example embodiments

[0035]FIG. 5 illustrates an example system 500 comprising devices 402a-g having multiple I / O interfaces 404a-t according to an embodiment of the invention. Devices 402 are connected via packet-switching network 502. If communication between devices 402 does not algorithmically require use of a strictly ordered topology, for example a PCI topology, data packets can be routed in random order through more than one of the multiple I / O interfaces of devices 402. In system 500 devices 402 are peers. When a PCI topology or similar “producer-consumer” topology is required, tree topology 504 is pre-configured such that device 402a functions as a root and devices 402b-g function as intermediate bridges or leaves.

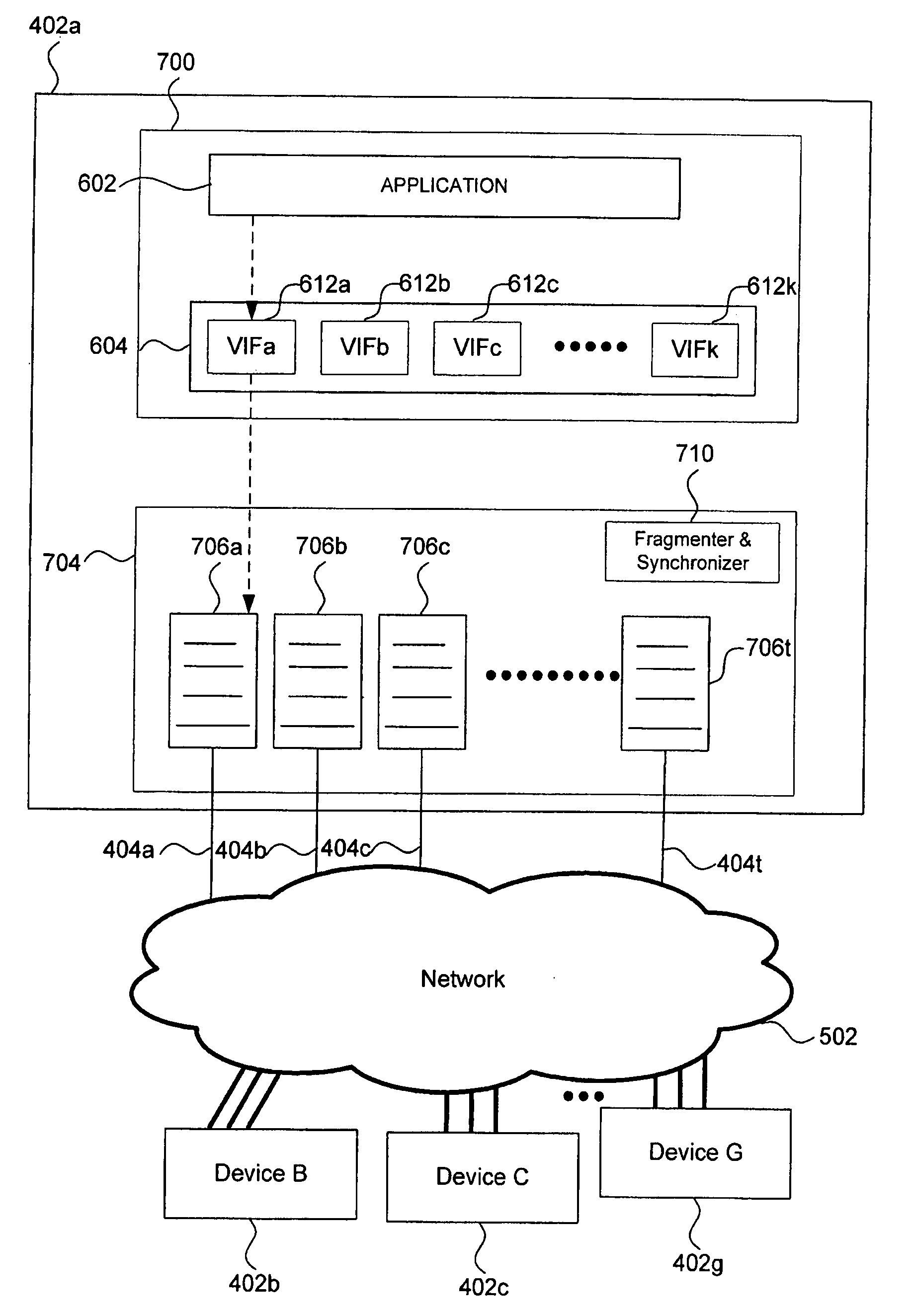

[0036]FIG. 6 illustrates an exemplary communication stack 600 according to an embodiment of the invention. Communication stack 600 comprises five layers 602-610 with application layer 602 being the top layer. Application layer 602 sends and receives data to / from shim layer 604. Shim l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com