System and method for CMP having multi-pressure zone loading for improved edge and annular zone material removal control

a technology of annular zone and multi-pressure zone, applied in the direction of grinding machine components, grinding machines, manufacturing tools, etc., can solve the problems of inability to solve the problem simultaneously, and inability to meet the requirements of the application

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

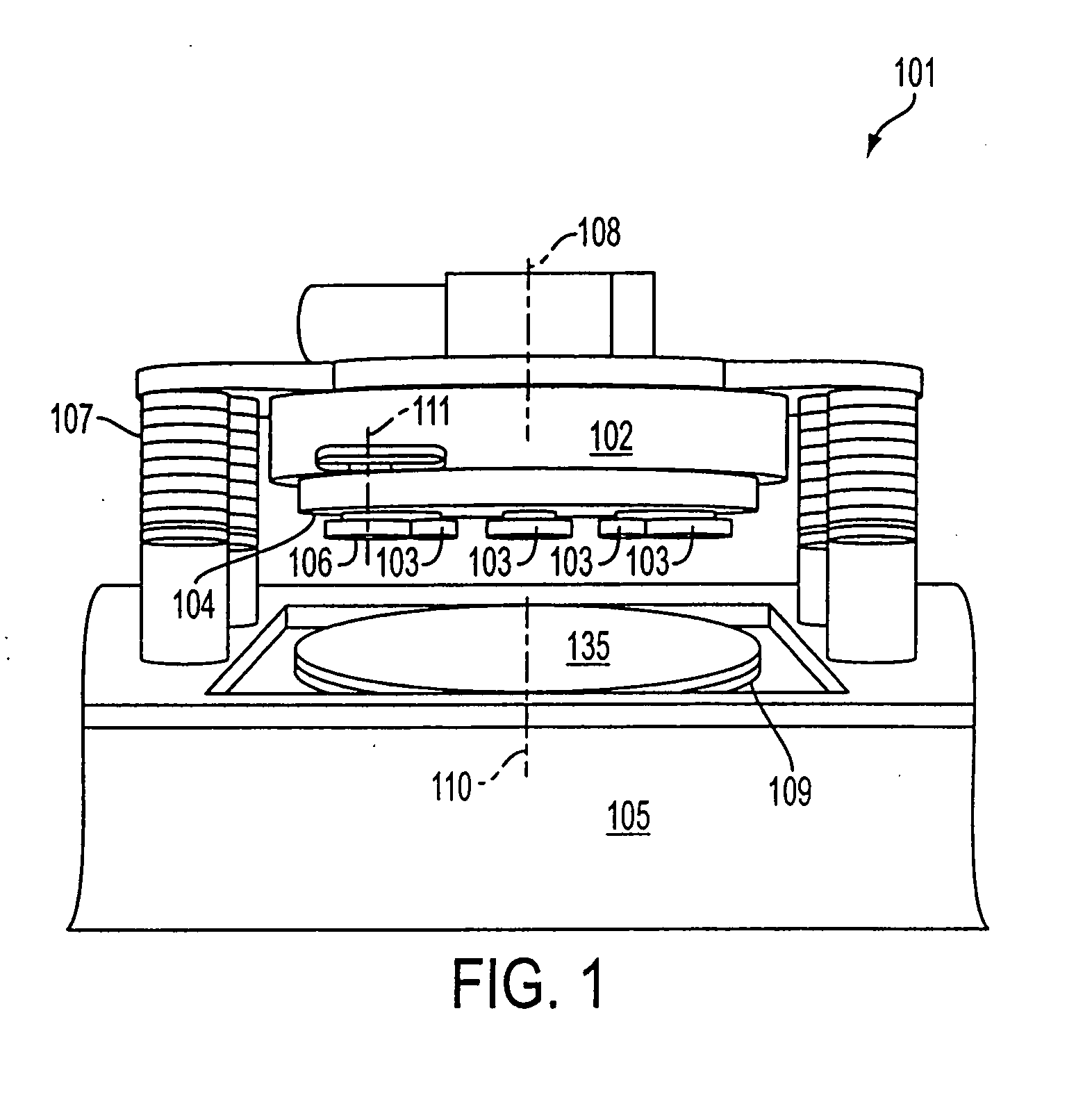

[0037] The inventive structure and method are now described in the context of specific exemplary embodiments illustrated in the figures. The inventive structure and method eliminate many of the problems associated with conventional head designs using polymeric insert between the backside of the wafer and the surface of the wafer subcarrier as well as problems associated with pressure distribution over the surface of the wafer for soft-backed heads. The different forces or pressures impart different loading of the front side surface of the wafer against the polishing pad resulting in a different rate of removal. The pressure applied to a retaining ring similarly alters the loading force of the retaining ring contact surface against the retaining ring and influences material removal at the edge of the wafer. The inventive structure and method replace the insert with a flexible film or membrane adjacent the back side surface of the wafer. In one embodiment, this membrane forms a sealed...

PUM

| Property | Measurement | Unit |

|---|---|---|

| sizes | aaaaa | aaaaa |

| pressures | aaaaa | aaaaa |

| pressures | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com