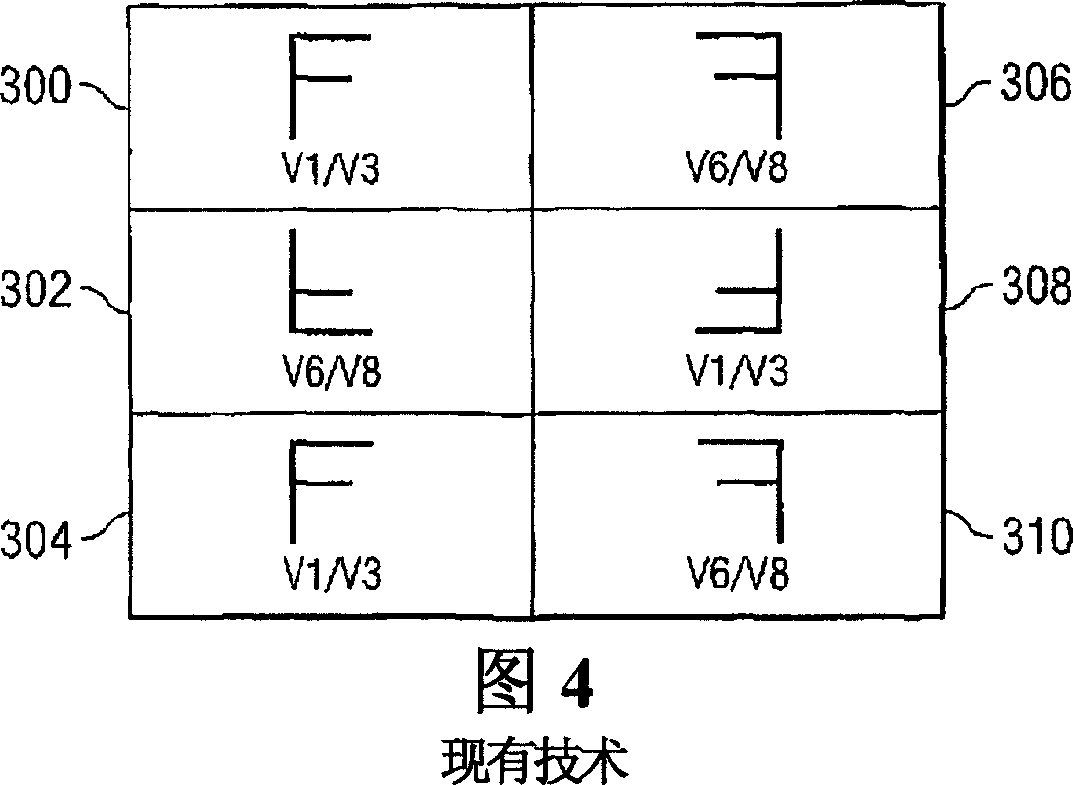

Staggered memory cell array

一种存储器单元、阵列的技术,应用在静态存储器、数字存储器信息、信息存储等方向,能够解决阵列尺寸限制等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030]Referring to FIG. 17, there is shown a block diagram of a radiotelephone as an example of a portable electronic device that may advantageously use the present invention for memory arrays, decoding circuits, interconnection units, or any other known in the art. in other geometric arrays. The radiotelephone includes antenna 1700 , radio frequency transceiver 1702 , baseband circuitry 1710 , microphone 1706 , speaker 1708 , keypad 1720 and display 1722 . The radiotelephone is preferably powered by a rechargeable battery (not shown) as is well known in the art. Antenna 1700 enables the radiotelephone to interact with the radio frequency environment in a manner known in the art for wireless communication. The radio frequency transceiver 1702 transmits and receives radio frequency signals through the antenna 1702 . The transmitted signal is modulated by the voice / data output signal received from the baseband circuit 1710 . The received signal is demodulated and provided to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com