Output stage structure

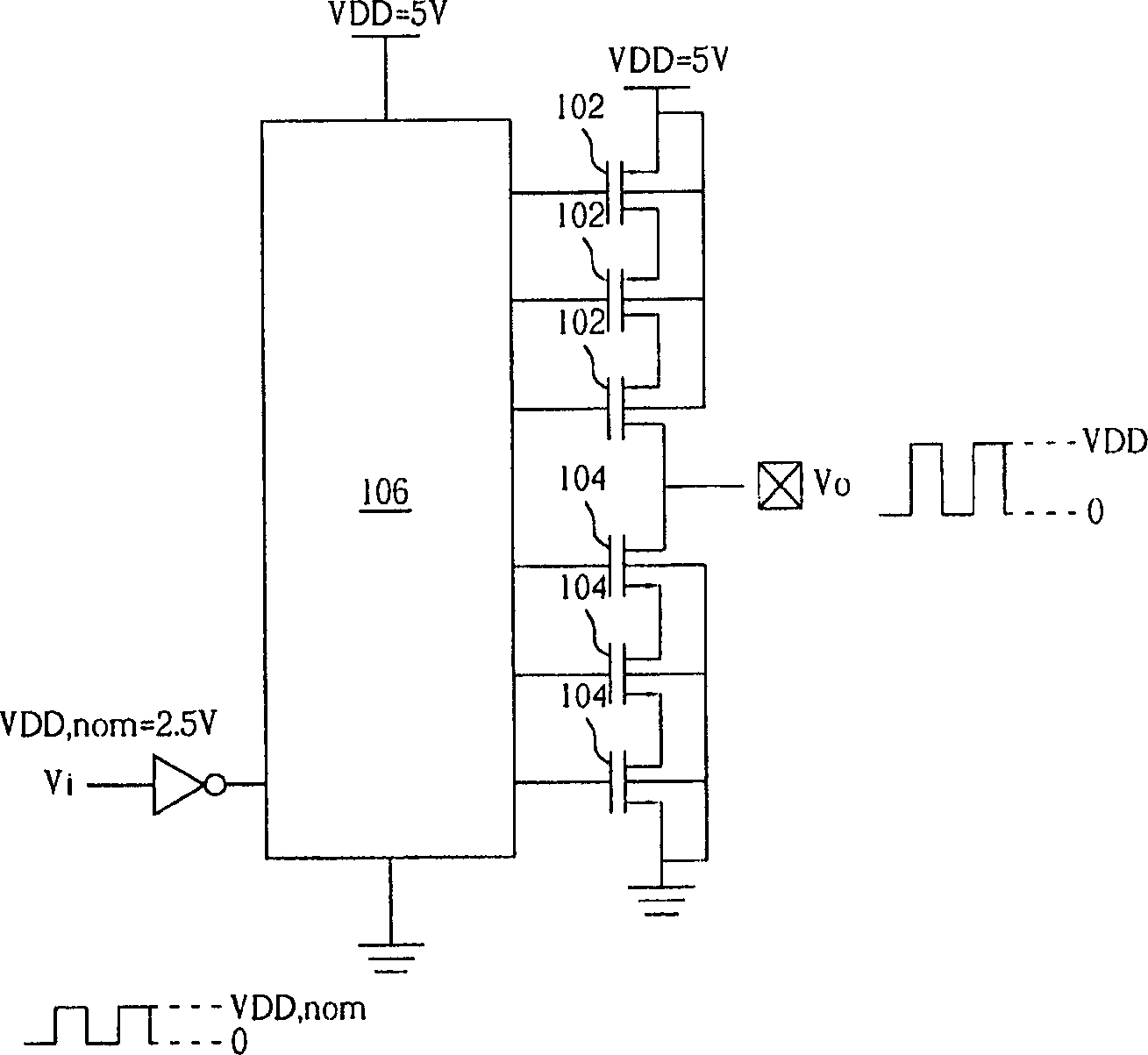

An output stage, metal technology, applied in the field of complementary metal oxide semiconductor transistor output stage structure, can solve the problem that the bias voltage cannot be controlled independently

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

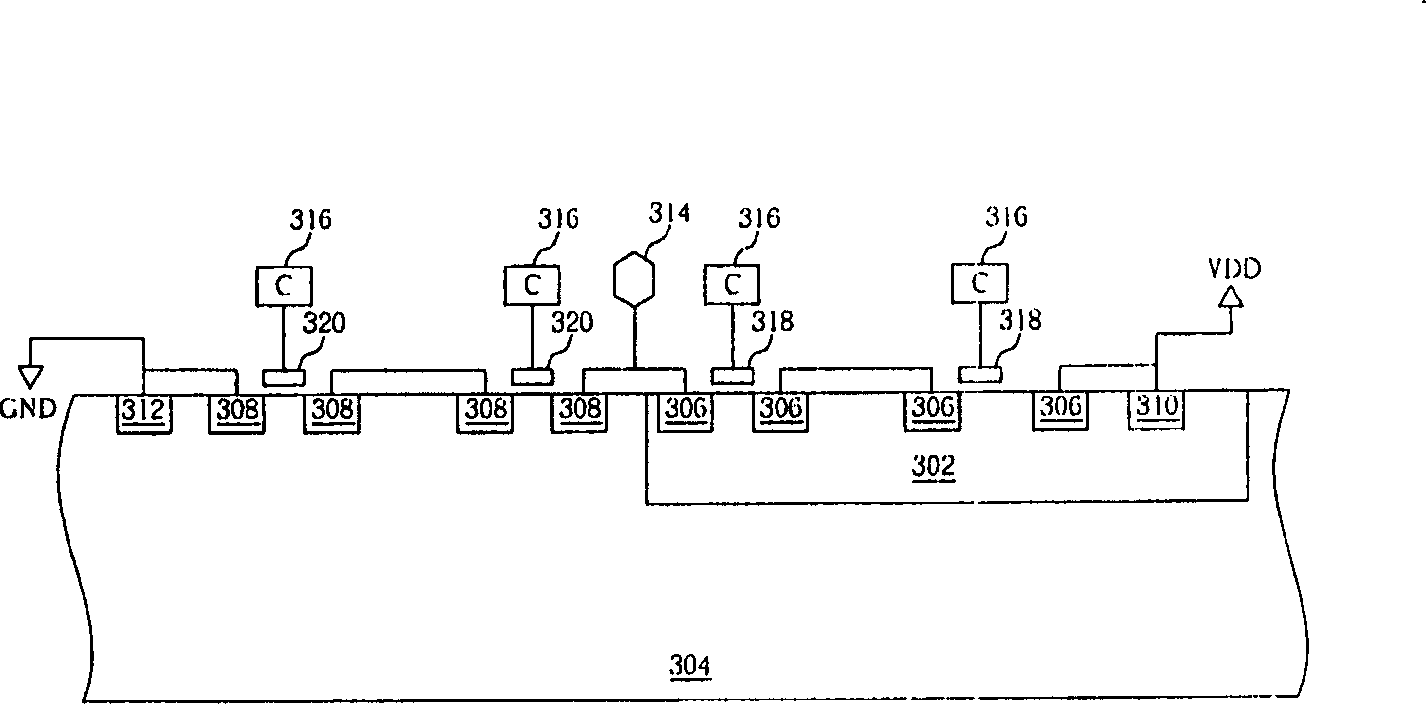

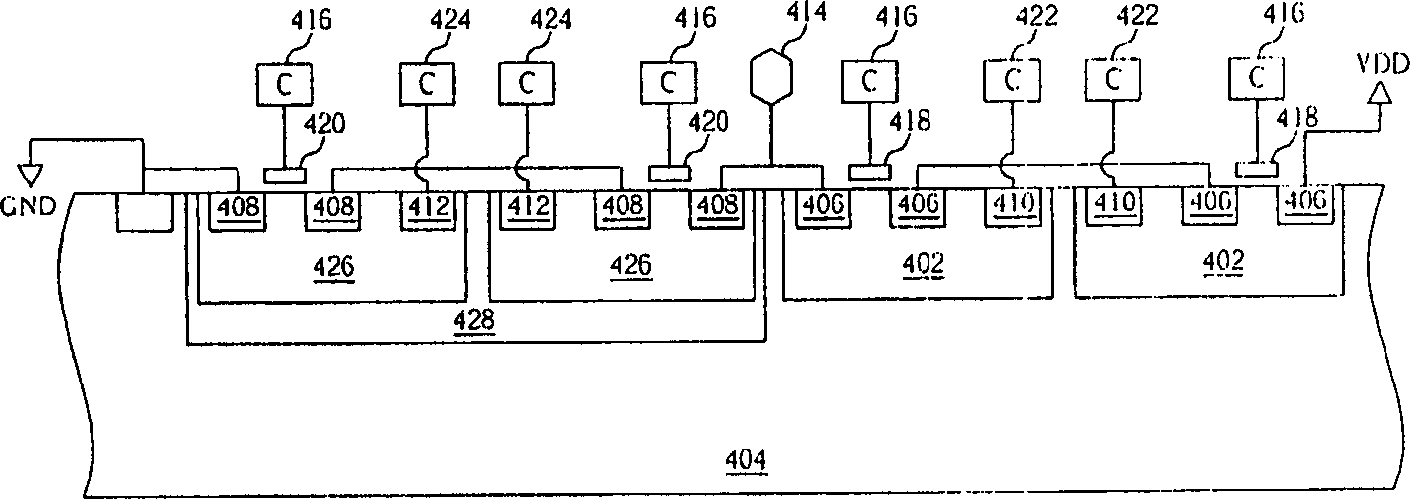

[0031] In the embodiment of the present invention, the high withstand voltage output stage is manufactured with a twin well (Twin well) process, so each NMOS transistor or PMOS transistor element has its own separate well area (Well), and users can Bias voltages are applied to the terminals of the substrate respectively, so that the voltage difference on the junction in the well region can be controlled to be reduced, so that the overall output stage is no longer limited by the junction breakdown voltage.

[0032] Please refer to image 3 , image 3 It is a schematic cross-sectional view of a high withstand voltage output stage structure according to an embodiment of the present invention. image 3As shown in FIG. 2 , a plurality of NMOS transistor elements and a plurality of PMOS transistor elements are fabricated on a p-type substrate (p substrate) 404 in a double well process. There are a plurality of separate n-type wells (n wells) 402 on the p-type substrate 404, and tw...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com