D/A converter and conversion method with compensation to reduce clock jitter

A technology of analog converter and analog conversion, which is applied in the direction of digital-to-analog converter, analog-to-digital converter, and data exchange through path configuration, which can solve the problems of complex design of analog front-end circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

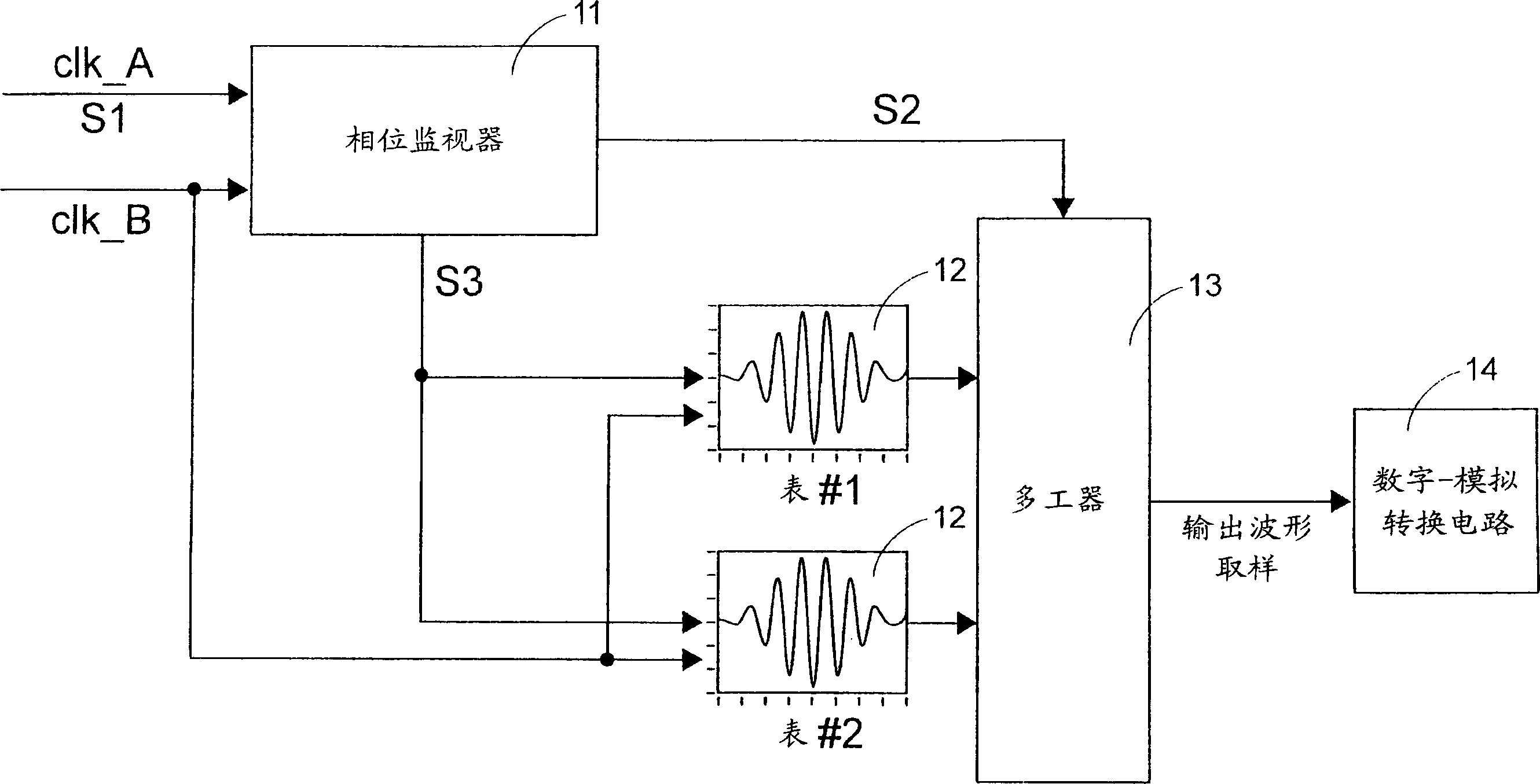

[0023] When a digital-to-analog converter is used in a common digital transmission system to convert data from a digital format to an analog format, the frequency of the driving (digital-to-analog conversion) clock is usually the same as the system clock or an integer multiple of the system clock, otherwise, When the transmission continues, the transmitted waveform pulse will gradually deviate from the ideal timing. In addition to the jitter of the system clock itself, the jitter of the transmitted waveform is added. This jitter is caused by the difference between the system clock and the digital-to-analog conversion clock. The frequency difference is the so-called out-of-sync, and the maximum value of jitter can usually be as large as one digital-to-analog conversion period. Now we use figure 1 Describe how to reduce the jitter of the system according to the present invention.

[0024] We assume that the period of the system clock clk-A is T A , while the period of the digit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com