Method for synchronizing timing output signal in digital communication equipment

A technology of clock output and synchronization processing, applied in digital transmission systems, synchronization devices, transmission systems, etc., to achieve the effect of ensuring continuity and smooth switching

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

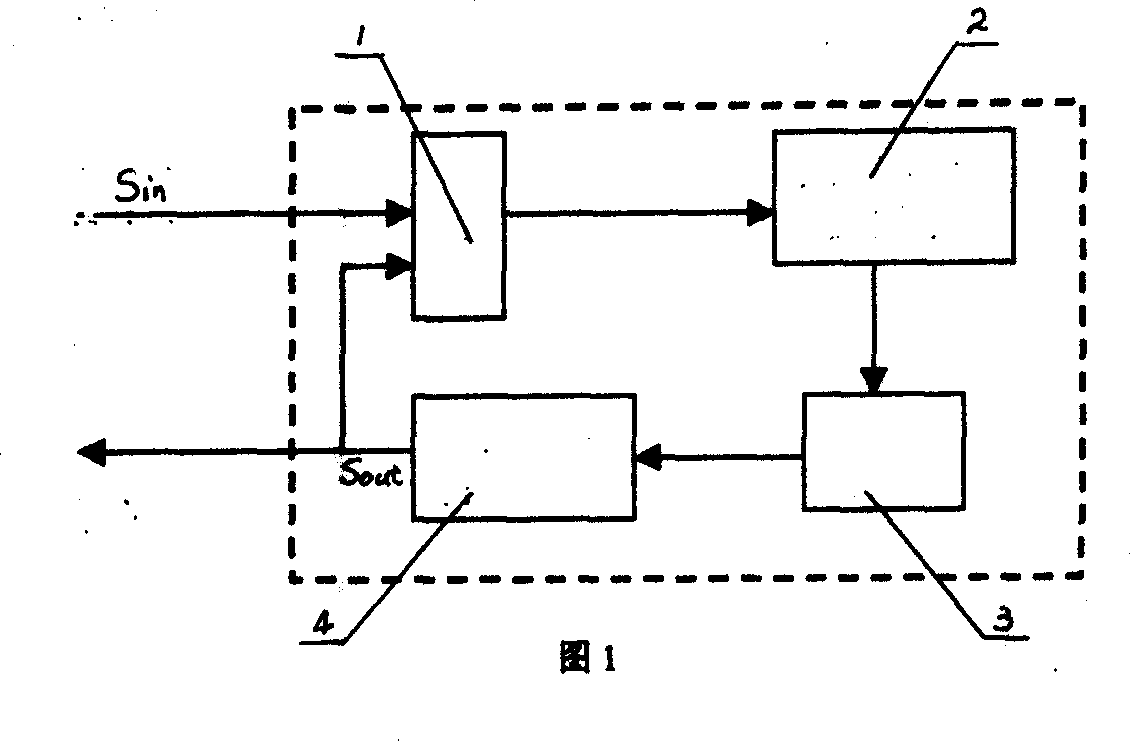

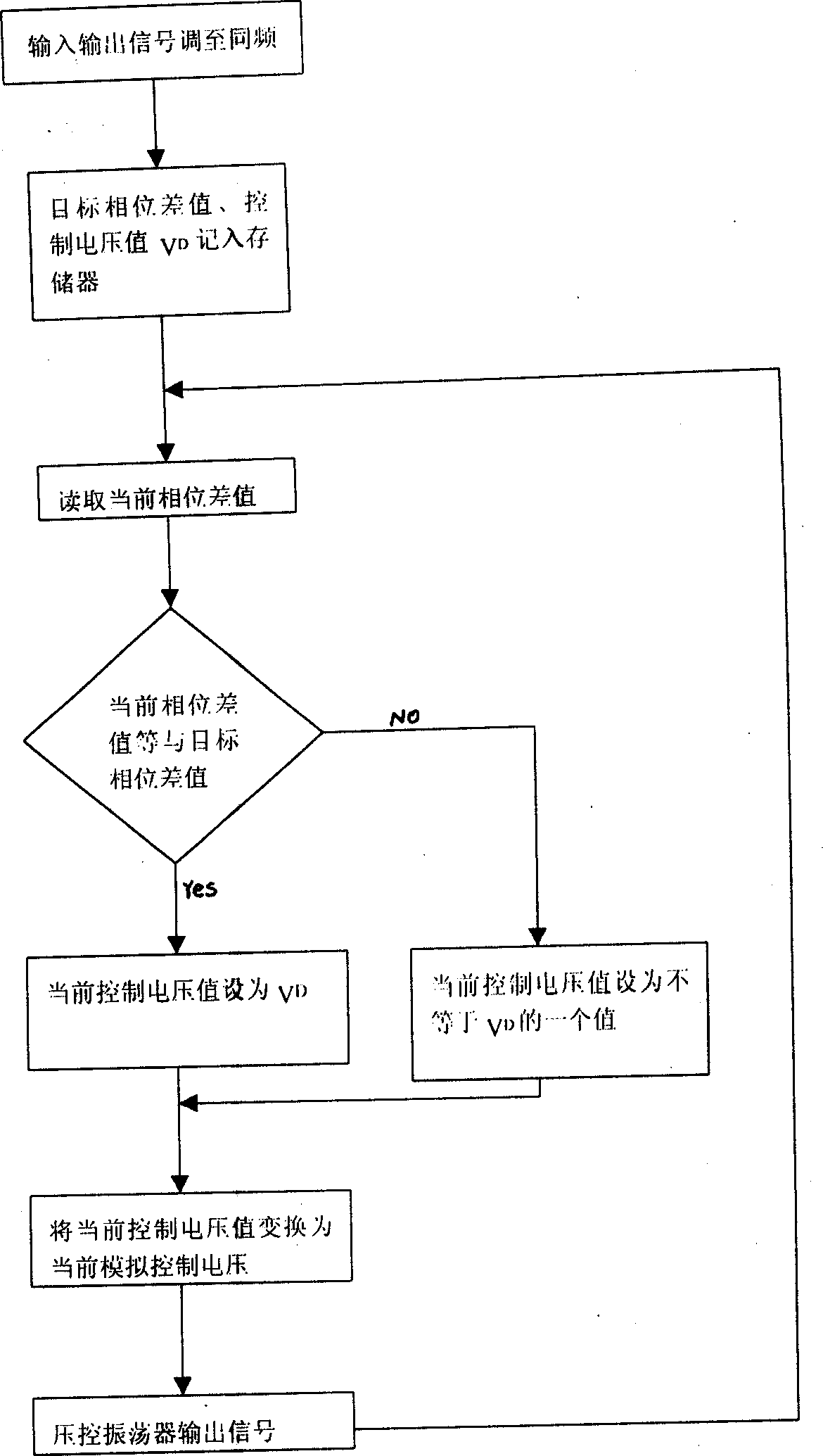

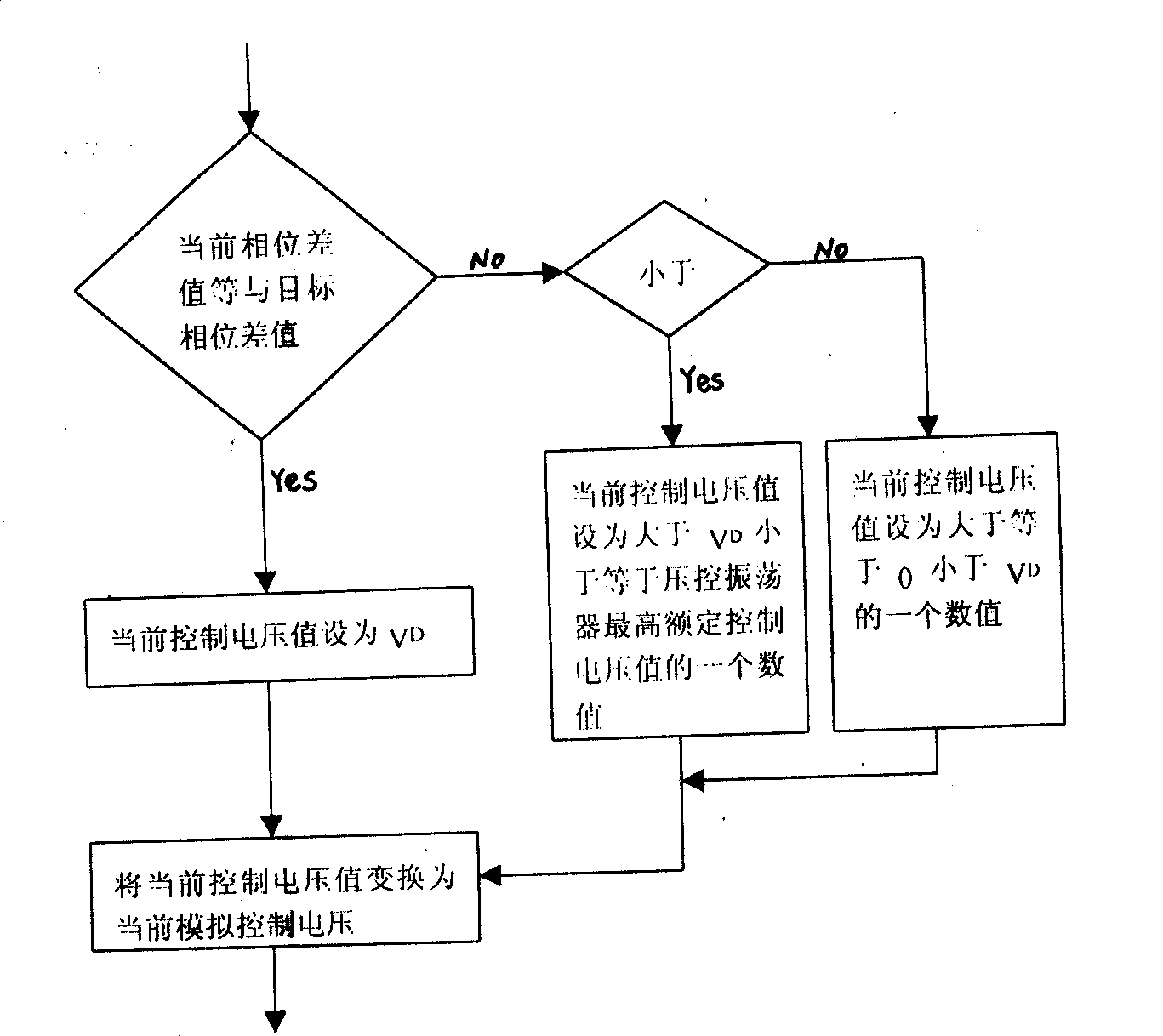

[0020] Refer to attached picture. The synchronous processing method of the clock output signal in the digital communication equipment of the present invention, it utilizes the digital phase-locked loop to adjust the clock output signal Sout to the same frequency as the clock input signal Sin, and the digital phase-locked loop is composed of phase detector 1, digital The loop filter controller 2, the digital-to-analog converter 3, and the voltage-controlled oscillator 4 are composed. After the target phase difference between the clock output signal and the clock input signal, such as 180 degrees, and the control voltage value V of the voltage-controlled oscillator after the clock output signal and the clock input signal have the same frequency D After being recorded in the memory of the digital loop filter controller in the digital phase-locked loop, the following cyclic steps are executed in sequence:

[0021] (1) The digital loop filter controller reads the current phase dif...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com