Data pack preprocessing method and bus interface and data processing unit thereof

A bus interface unit and processing unit technology, applied in the direction of electrical digital data processing, bus network, data exchange network, etc., can solve the problem of performance degradation and achieve the effect of software simplification

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

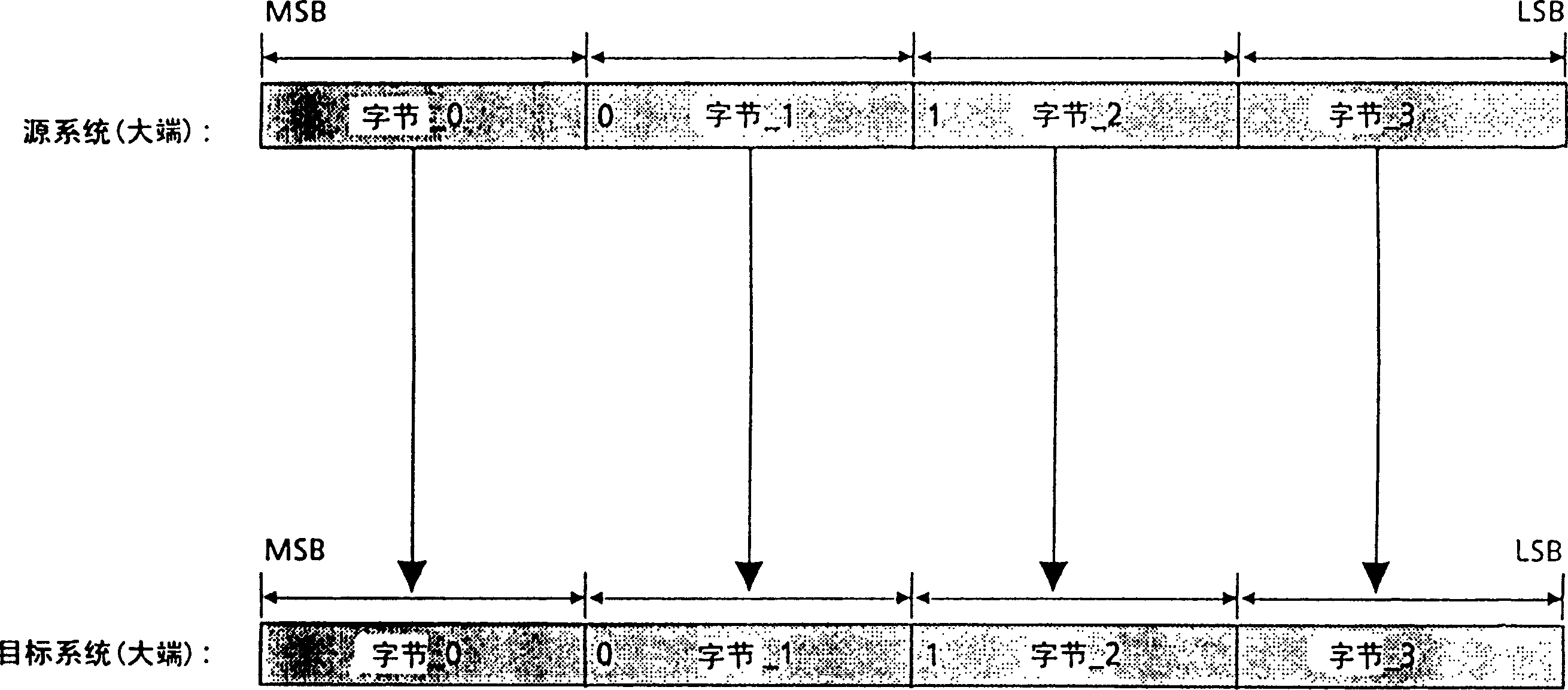

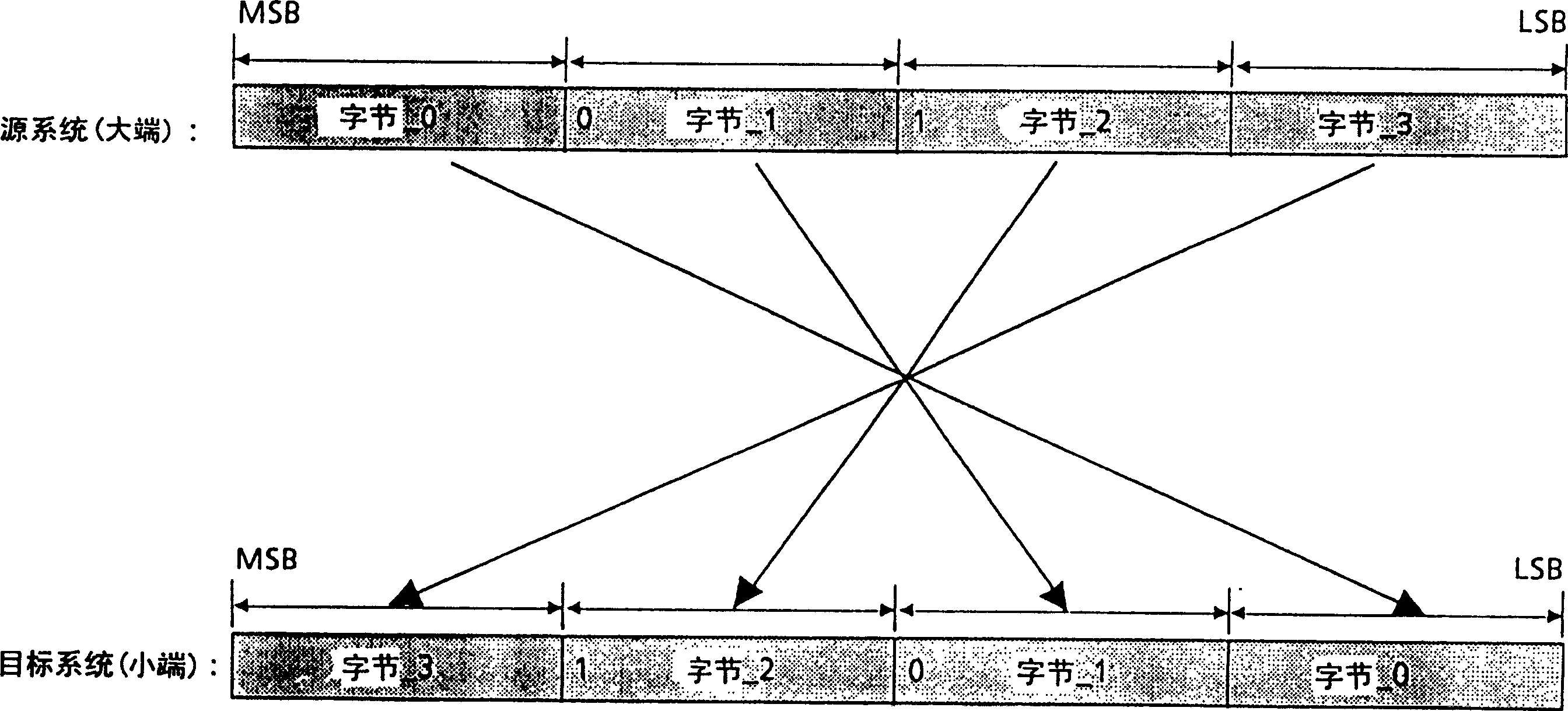

[0032] First, explain the meaning of the two words big endian and little endian.

[0033] Big-endian and little-endian are two terms that describe the order in which a sequence of bytes is stored in computer memory. Big endian is the order in which "big endian" (the most significant byte value in the sequence) is stored first (lowest bit storage address). Little endian is the order in which "little endian" (the least significant byte value in the sequence) is stored first. For example, in a big-endian computer, the hexadecimal number 0x4F52, the required two bytes, is stored in the memory as 0x4F52 (for example, 0x4F) is stored at address 1000, and 0x52 will be stored as 0x524F (0x52 at address 1000, 0x4F at address 1001).

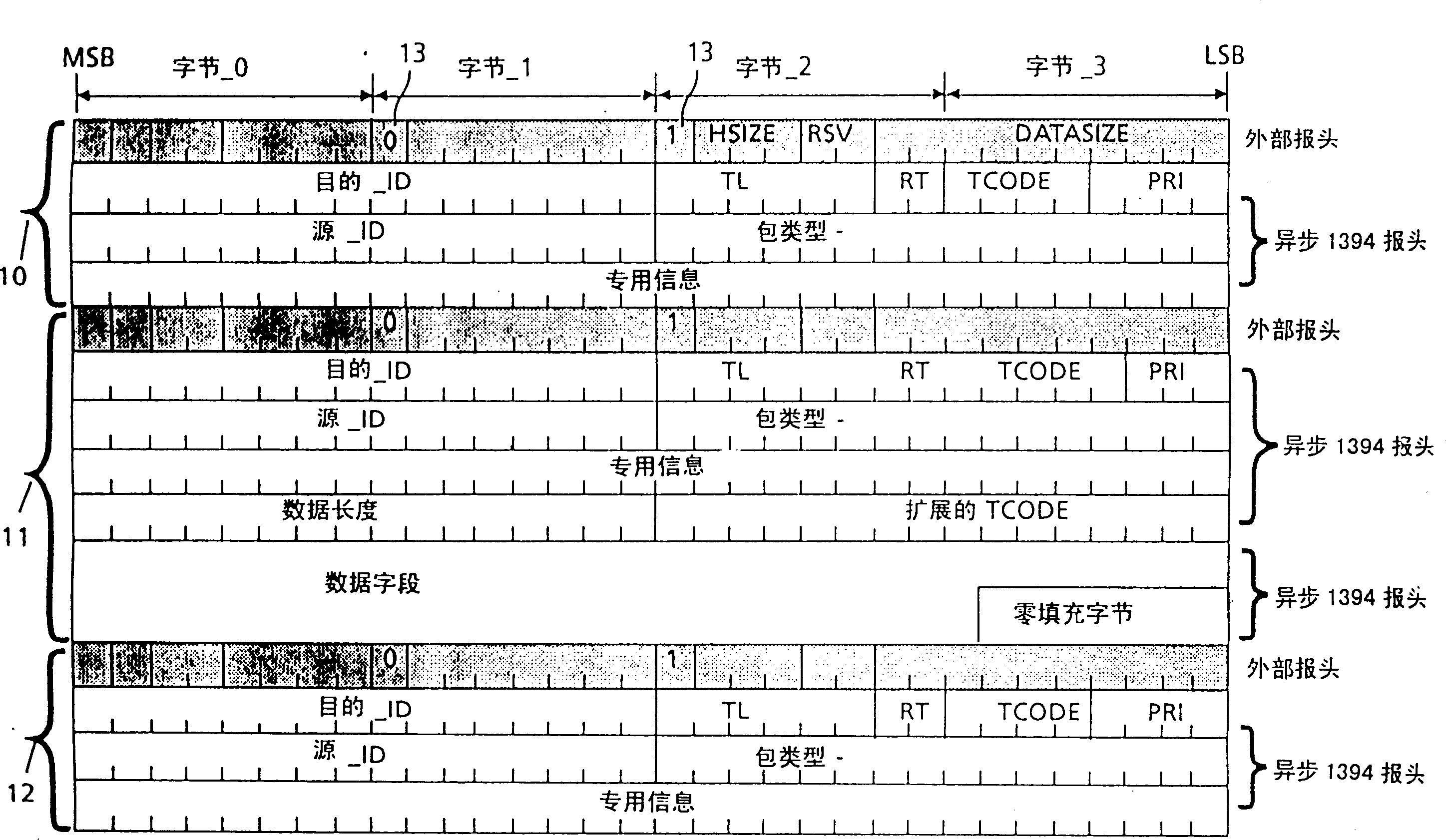

[0034]As already stated above in the introduction, multi-byte data words are often present in electronic devices. A quad segment data word consisting of 4 bytes or corresponding 32 bits is an example. For example, the IEEE1394 bus is structured in a pl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com