A circuit and method for realizing PCIE resource automatic allocation and a storage medium

A technology for automatic allocation and resource allocation. It is applied in resource allocation, electrical digital data processing, instruments, etc. It can solve the problems of wasting server PCIE resources, unable to provide PCIE interface of CPU, and affecting the data transmission efficiency of server processors and storage devices.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

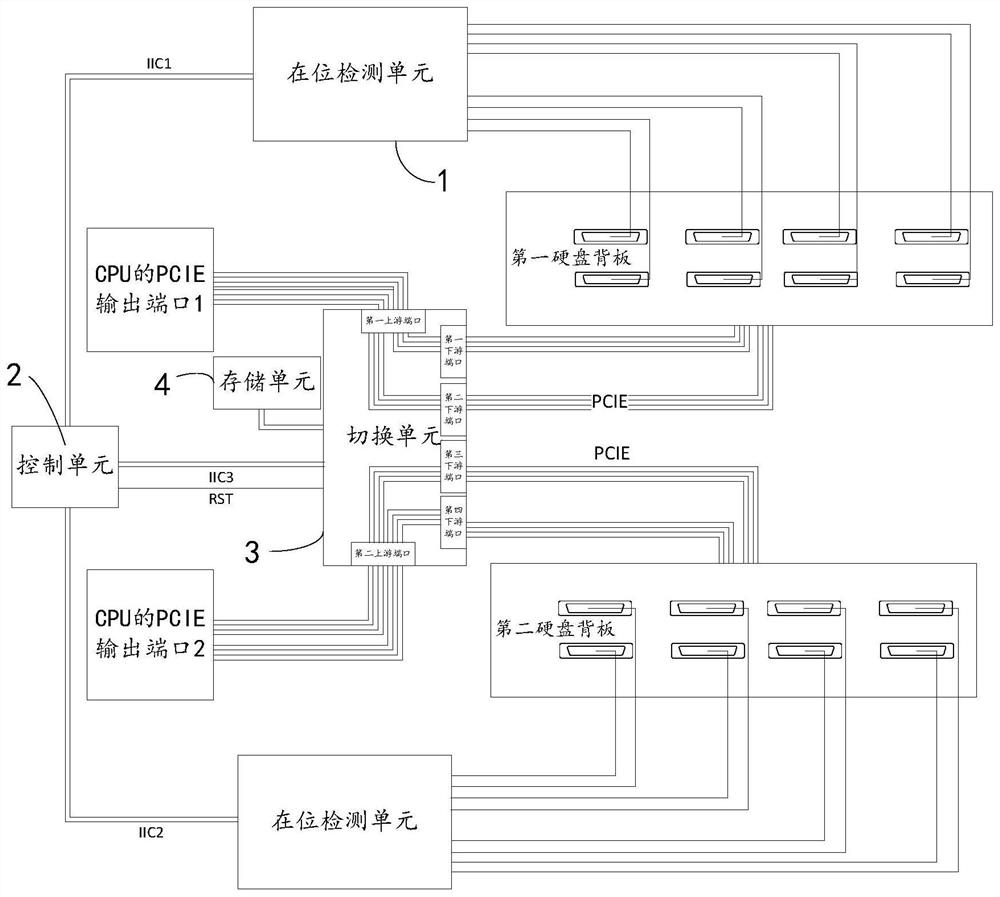

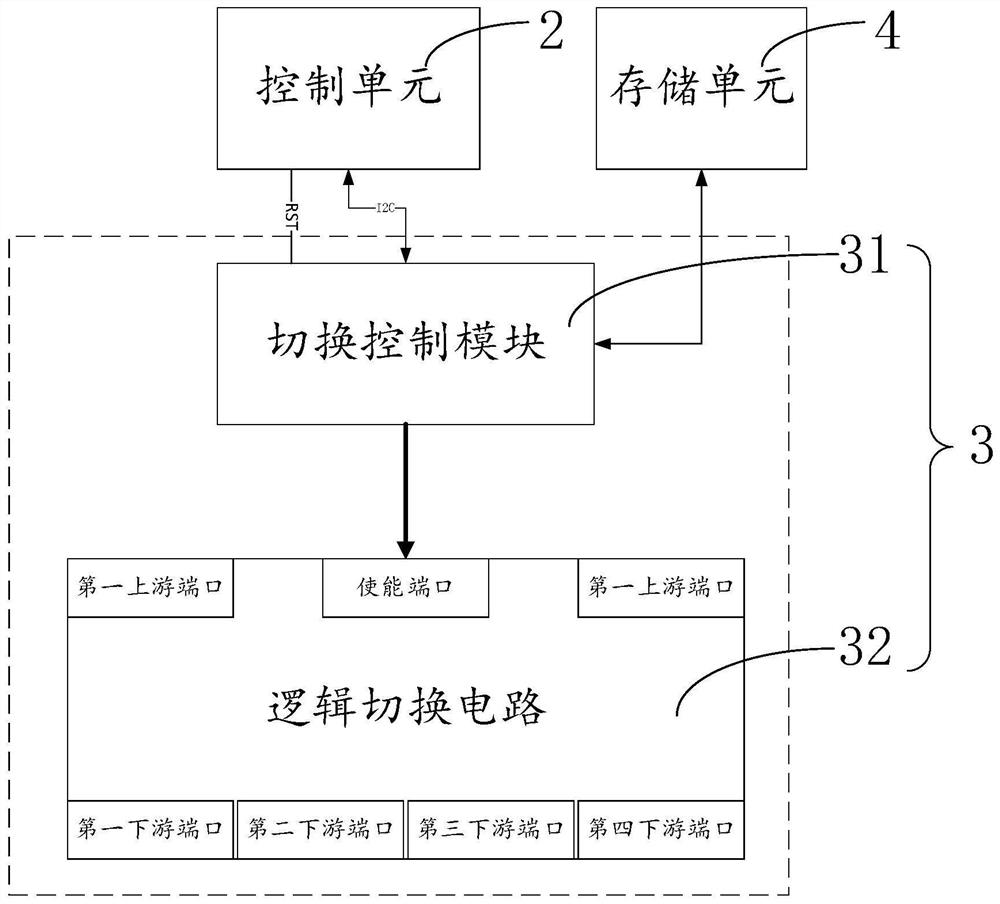

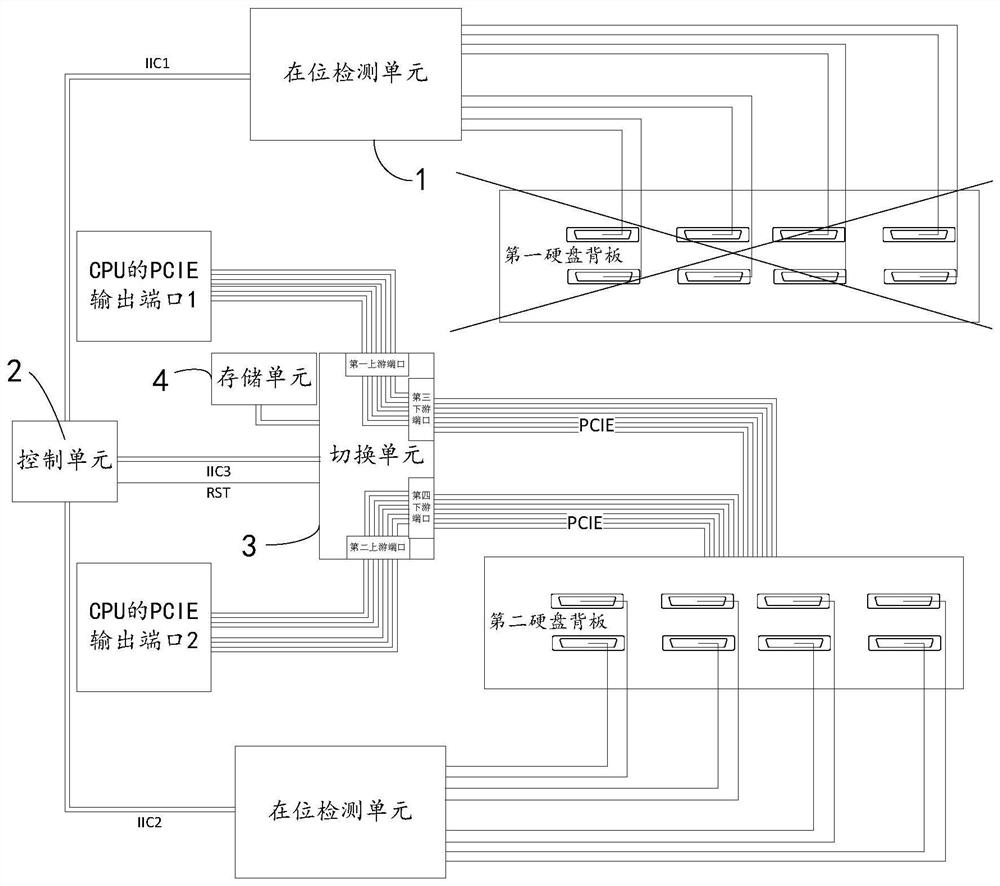

[0048] refer to figure 1 As shown, the embodiment of the present application provides a circuit for realizing automatic allocation of PCIE resources, including:

[0049] Electrically connected to several in-position acquisition units 1 of the presence indication circuits of the first hard disk backplane and the second hard disk backplane; in this embodiment, the first hard disk backplane and the second hard disk backplane respectively pass 8 hard disk interfaces are connected to 8 hard disks, and each hard disk interface is respectively provided with an in-position indicating circuit; The in-position acquisition unit 1 sends a first level signal; when the hard disk interface on the hard disk backplane is plugged with a hard disk, the in-position indicating circuit sends a second level signal to the in-position acquisition unit 2 .

[0050] Several described in-position acquisition units 1 are connected to control unit 2 by bus, in the specific implementation process, describe...

Embodiment 2

[0064] This embodiment provides a method for realizing automatic allocation of PCIE resources, see Figure 5 As shown, the method for realizing the automatic allocation of PCIE resources includes:

[0065] S100, the in-position acquisition unit acquires the in-position information of the hard disk on the hard disk backboard according to the output signal of the in-position indicating circuit;

[0066] S200, the control unit polls each of the in-position acquisition units to acquire the in-position information of the hard disk on each hard disk backboard;

[0067] S300, the control unit sends the corresponding presence information to a corresponding switching unit;

[0068] In the specific implementation process, the switching unit and the in-position acquisition unit are configured with a unique identification address, and the control unit configures a mapping table between the switching unit and the in-position acquisition unit, and the mapping table will be corresponding in...

Embodiment 3

[0084] This embodiment provides a storage medium for realizing automatic allocation of PCIE resources. The storage medium for realizing automatic allocation of PCIE resources stores at least one instruction, and executing the instruction implements the described method for realizing automatic allocation of PCIE resources.

[0085] The circuit provided by the application to realize the automatic allocation of PCIE resources is connected to the PCIE output port of the server CPU through the first upstream port and the second upstream port of several switching units 3; through the first downstream port and the second downstream port of the switching unit 3 The hard disks on the first hard disk backboard are connected, and the hard disks on the second hard disk backboard are connected through the third downstream port and the fourth downstream port of the switching unit 3 . The signals of the in-position indicating circuits of the hard disks on several first hard disk backplanes an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com