Matcher output power debugging method and debugging system

A technology of output power and debugging method, which is applied in the direction of discharge tubes, electrical components, circuits, etc., can solve the problems of inability to adjust at one time, waste of resources and time, etc., and achieve the effect of shortening debugging time, reducing debugging costs and reducing resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

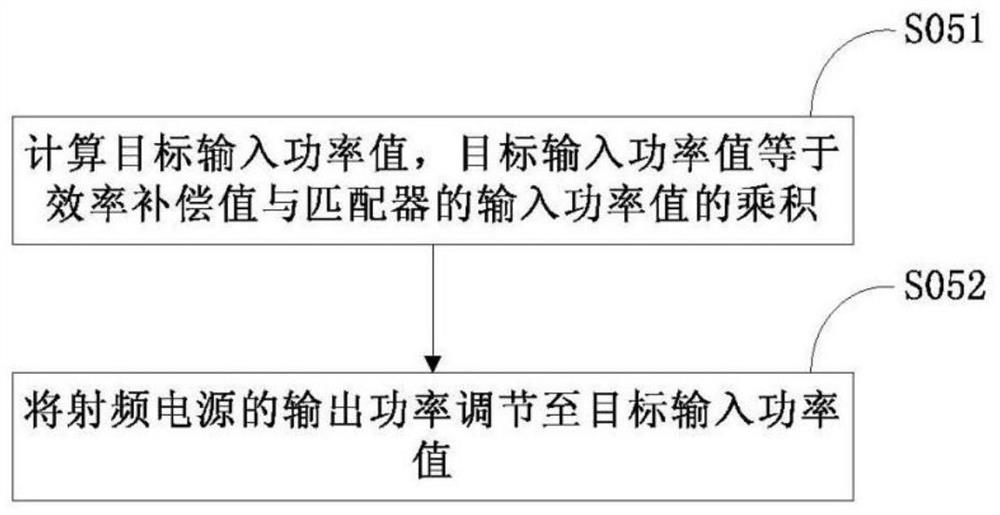

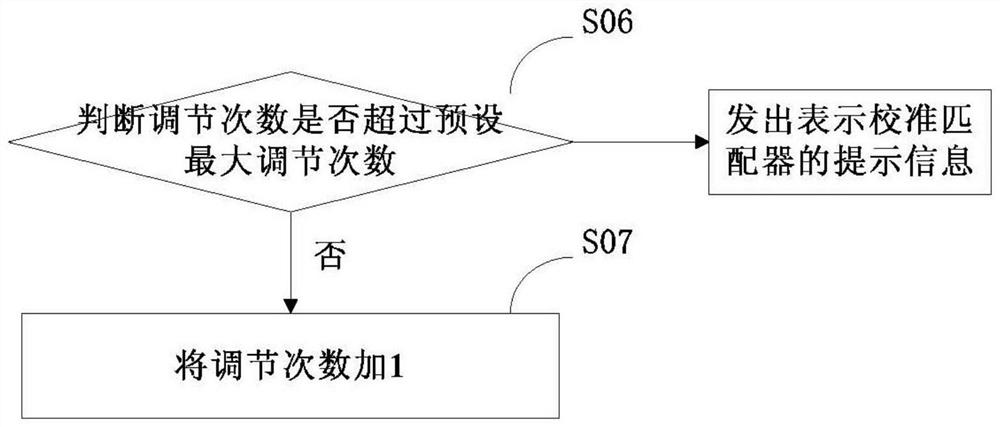

[0038] In order to realize the object of the present invention, a method for debugging the output power of a matcher is provided. Specifically, the input end of the matcher is electrically connected to the output end of the RF power supply, and the output end of the matcher is electrically connected to the RF power receiving end of the process chamber (such as the upper electrode coil or the lower electrode of the process chamber); The device is used to feed the RF power output by the RF power supply into the reaction chamber. However, since the matcher has a certain loss of its own, the actual power fed into the reaction chamber through the matcher will be far from the actual output power of the RF power supply, and the losses of different matchers are different. If different matchers are put into use, the quality consistency of the manufactured wafers cannot be guaranteed. In order to solve the above technical problems, such as figure 1 As shown, the debugging method provi...

Embodiment 2

[0075] This embodiment provides a debugging system for debugging the output power of the matcher, such as Figure 6 As shown, it includes a power detection unit 2 and a control unit 1 .

[0076] Wherein, the power detection unit 2 is used to detect the input power value of the input end of the matching device 4 and the output power value of the output end of the matching device 4 when the radio frequency power supply 3 is turned on, and send the input power value and the output power value of the matching device 4 to control unit 1. In some embodiments, when the matcher 4 is applied in the field of semiconductor processing, the input end of the matcher 4 is electrically connected to the output end of the radio frequency power supply 3. At this time, the input power value of the input end of the matcher 4 is the radio frequency The output power value of the power supply 3 ; the output end of the matcher 4 is electrically connected to the components (eg, the bottom electrode) i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com