Calibration controller for DDR3 storage protocol

A storage protocol, DDR3 technology, applied in program control, computer control, general control system, etc., can solve the problems of poor anti-interference ability of DDR3 calibration controller, poor sampling accuracy of DDR3 calibration controller, and clock deviation, etc. Sampling stability and high performance, fast and accurate phase selection, accurate and consistent phase effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

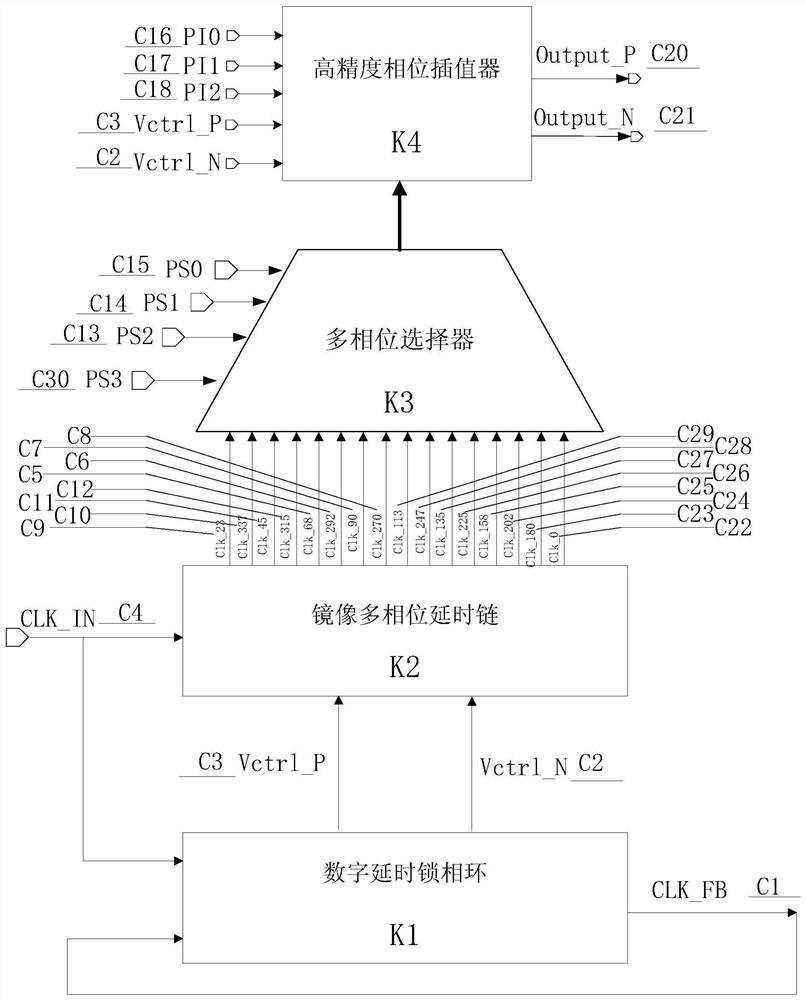

[0026] like figure 1 As shown, a calibration controller for the DDR3 storage protocol includes: a digital delay-locked loop K1, a mirrored multi-phase delay chain K2, a multi-phase selector K3 and a high-precision phase interpolator K4.

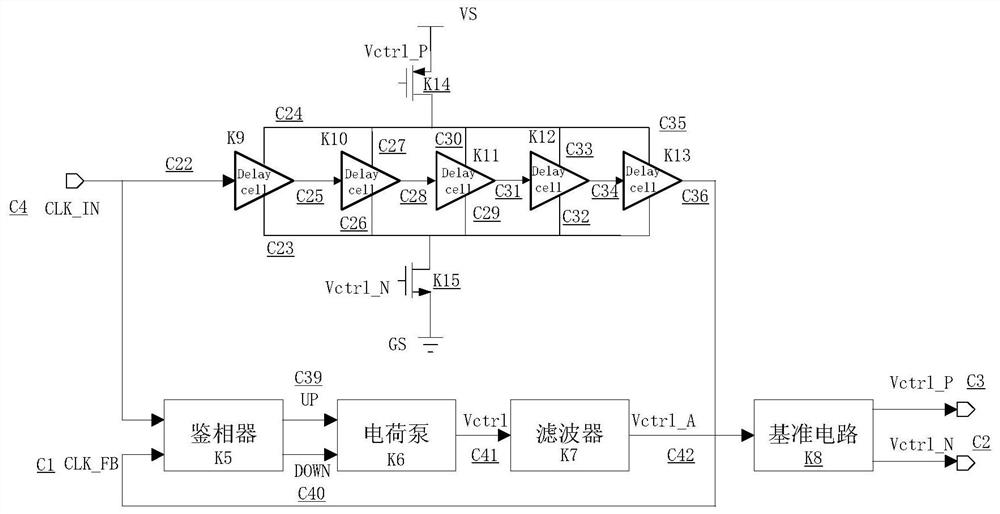

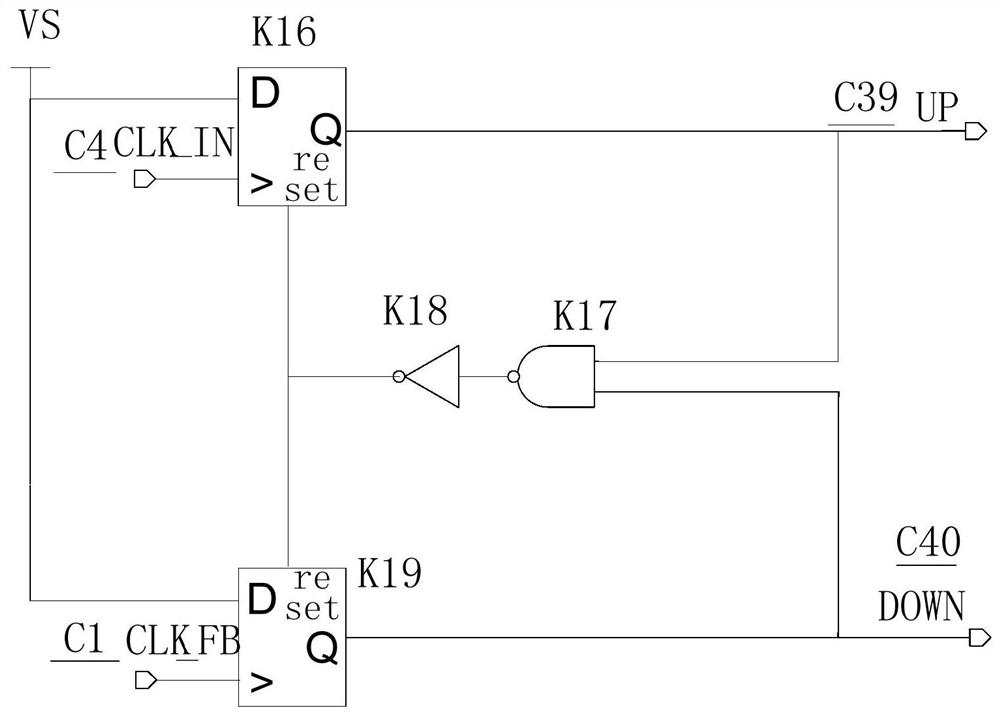

[0027] The digital delay phase-locked loop K1: receives the externally input clock signal CLK_INC4, locks and delays the input clock signal CLK_INC4, outputs the clock signal CLK_FBC1 and feeds back to the input of the digital delay phase-locked loop K1, and outputs the voltage signal Vctrl_PC3 and voltage signal Vctrl_NC2 to mirror multi-phase delay chain K2 and high precision phase interpolator K4;

[0028] Mirror multi-phase delay chain K2: Receive externally input clock signal CLK_INC4, receive voltage signal Vctrl_PC3 and voltage signal Vctrl_NC2 sent by digital delay phase-locked loop K1, convert into 16 output clock signals Clk_23C9, Clk_337C10, Clk_45C11, Clk_315C12, Clk_68C5 , Clk_292C6, Clk_90C7, Clk_270C8, Clk_113C29, Clk_247C28, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com