Manufacturing method of separation gate power MOSFET device

A manufacturing method and separation gate technology, which are used in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

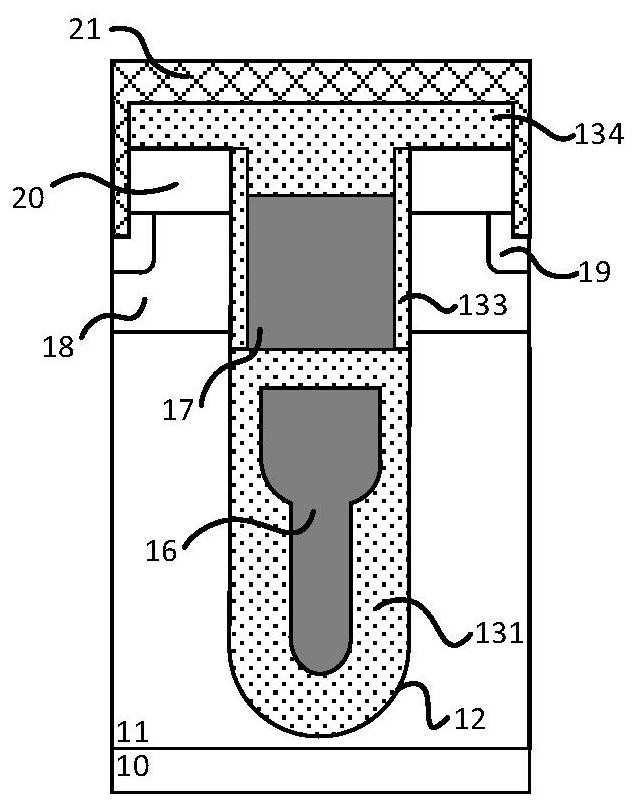

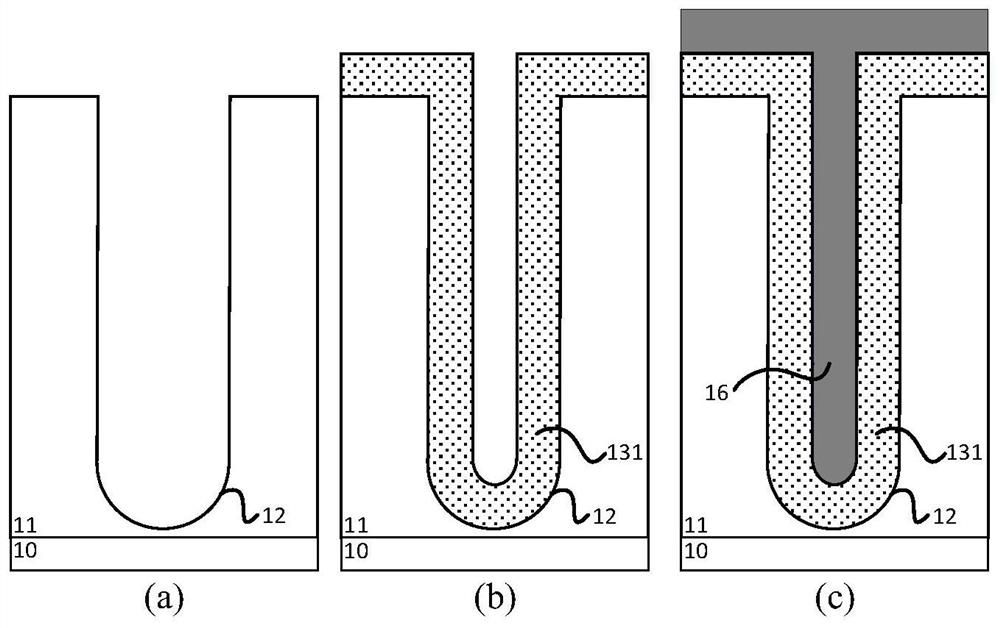

[0040] like image 3 As shown, a method for manufacturing a split gate power MOSFET device includes the following steps:

[0041] 1) A series of groove structures are formed on the epitaxial layer, and a first dielectric layer is formed on the inner wall of the groove structure;

[0042] 2) depositing polysilicon in the groove structure so that the polysilicon fills the entire groove;

[0043] 3) The polysilicon deposited in the etching step 2) forms the lower half of the stepped separation gate electrode in the control gate groove of the active region;

[0044] 4) wet etching the first dielectric layer, then depositing polysilicon in the groove structure, so that the polysilicon fills the entire groove;

[0045] 5) The polysilicon deposited in the etching step 4) forms the upper half of the stepped separation gate electrode in the control gate groove of the active region;

[0046] 6) depositing and etched back to form a second dielectric layer in the groove of the active reg...

Embodiment 2

[0061] like Figure 4 As shown, this embodiment provides some steps of a method for manufacturing a split-gate power MOSFET device, which is used to replace image 3 In the (j)-(k) process, the difference between this embodiment and the manufacturing method described in Embodiment 1 is that step 9) can be implemented as follows:

[0062] 9) dry etching the oxide layer, controlling the etched interface to keep a certain distance from the upper interface of the stepped separation gate; then wet etching away the remaining silicon nitride in the groove;

Embodiment 3

[0064] like Figure 5 As shown, the difference between this embodiment and the manufacturing method described in Embodiment 1 is that the first dielectric layer formed in step 1) surrounding the separated gate electrode adopts a low-k material with k less than 3.9 instead of silicon dioxide, which can further reduce the source-drain capacitance.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com