CT detector data transmission structure and CT detector data transmission method based on source synchronization LVDS-SERDES

A data transmission method and data transmission technology, applied in the field of CT detector data transmission structure based on source synchronous LVDS-SERDES, can solve the problem of high cost, and achieve the effects of strong applicability, cost reduction, and wide range of chip selection

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

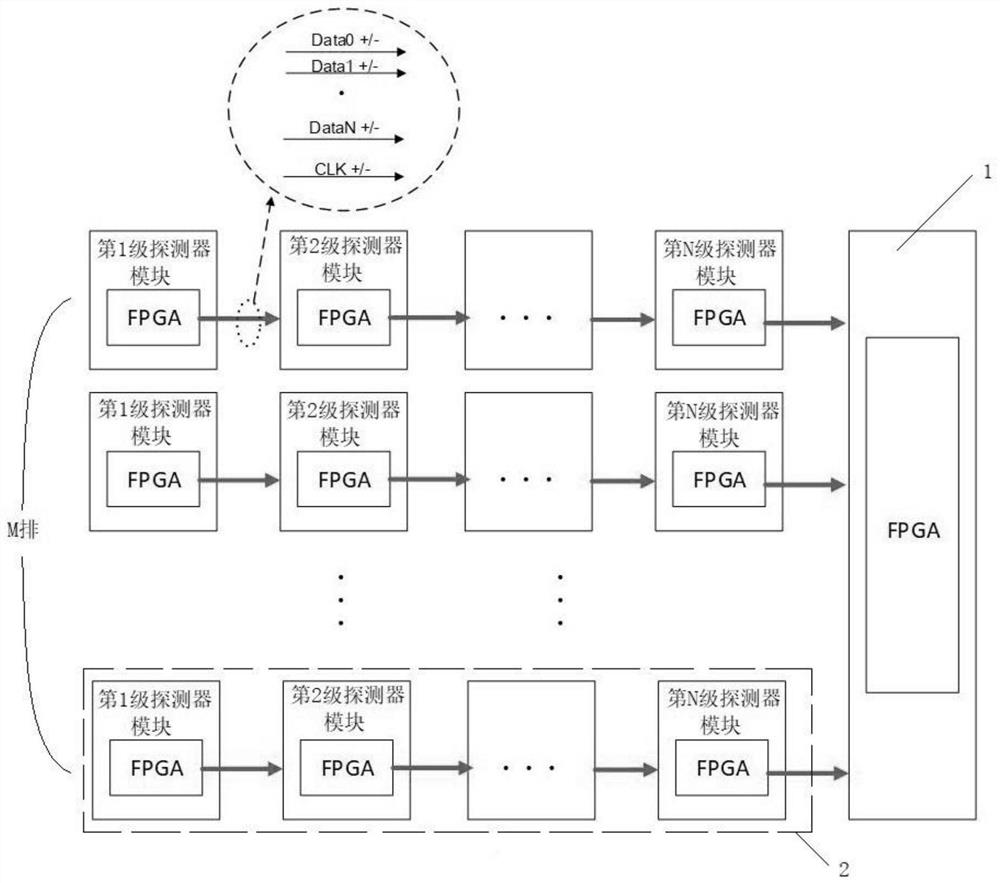

[0026] Such as figure 1 The shown CT detector data transmission structure based on source synchronous LVDS-SERDES includes data aggregation module 1 and M rows of detector groups 2, M≥2; each row of detector groups is connected to the data aggregation module; each row of detection Each detector group includes N detector modules, N≥2; in each row of detector groups, each detector module is serially connected; each detector module is equipped with an FPGA chip. Wherein, the value of M is usually 16 rows of detector groups, 64 rows of detector groups and 256 rows of detector groups. The invention can universally match the data transmission structure of detector groups with 16 rows, 64 rows, 256 rows or more.

[0027] Further, the detector groups in each row communicate with each other in parallel. The rows of detector groups in the structure of the present invention are in parallel, and the detector modules in each row of detector groups are in series. The present invention co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com