Method and device for debugging plug-in chip through SDIO interface, equipment and medium

A technology of interface debugging and chips, which is applied in the computer field, can solve problems such as debugging inconvenience, and achieve the effect of convenient operation and cost saving

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

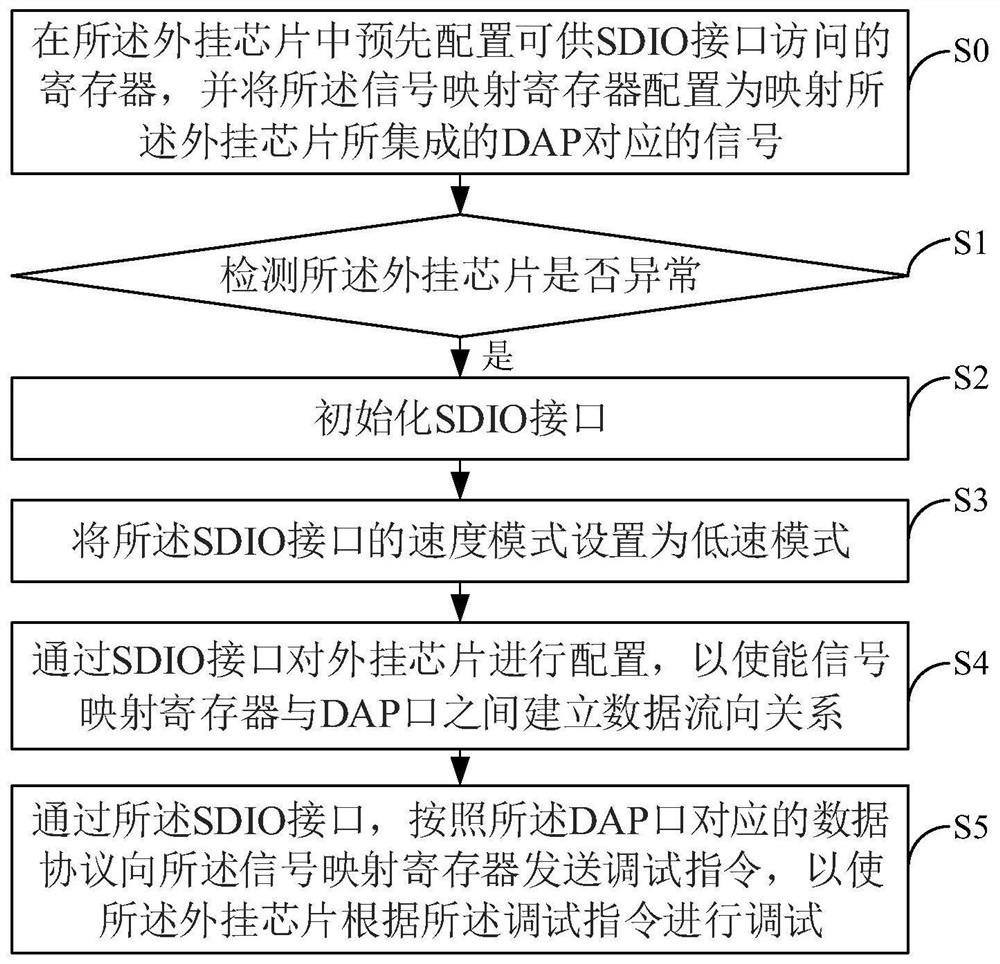

[0034] This embodiment provides a method for debugging a plug-in chip through an SDIO interface, which is suitable for a main control chip, and the main control chip communicates with the plug-in chip through an SDIO interface. like figure 1 As shown, the method includes the following steps:

[0035] S0, in the RFU (Reserved for Future Use, reserved for future use) subregion of the plug-in chip, pre-configure the registers (recorded as signal mapping registers) that can be accessed by the SDIO interface, and configure the signal mapping registers as Mapping the signals corresponding to the DAP integrated in the external chip.

[0036] In this embodiment, the external chip may be, for example, an ARM chip, and the ARM chip usually integrates a SWD interface as its DAP port. The SWD interface realizes the debugging of the ARM chip through a data line and a clock line, and its corresponding signals include data signals and clock signals.

[0037] On this basis, the signal mapp...

Embodiment 2

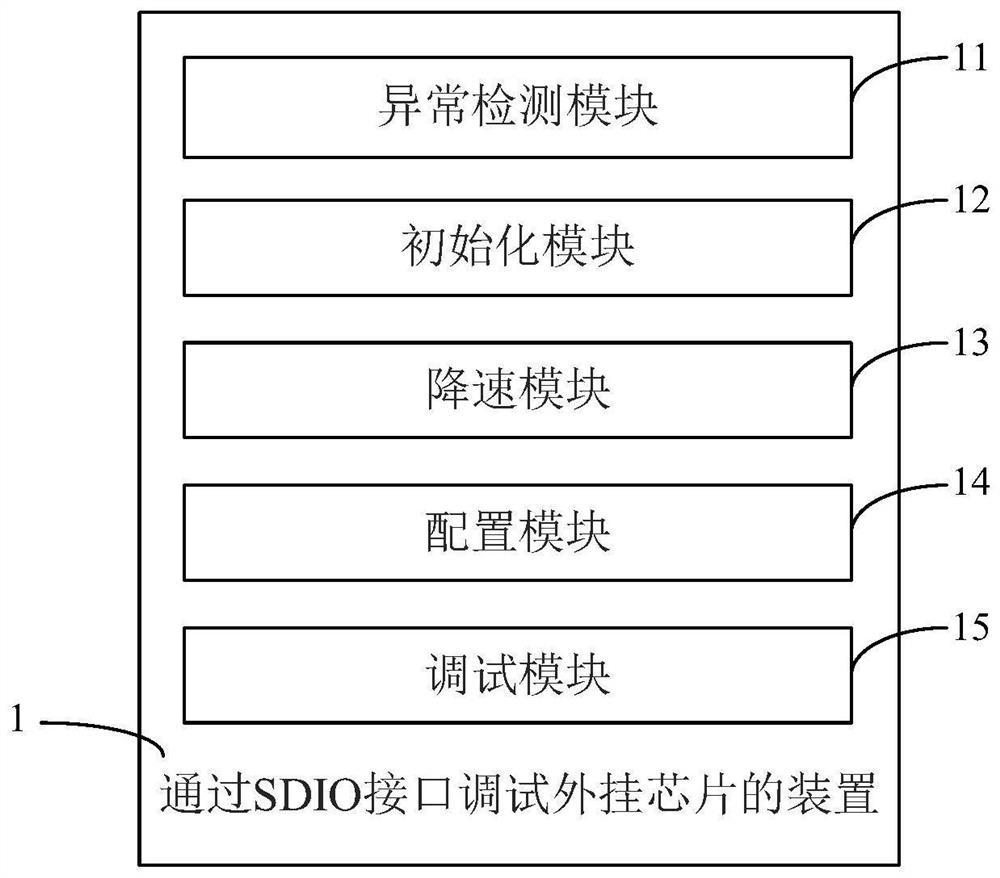

[0049] This embodiment provides a device for debugging a plug-in chip through an SDIO interface, which is suitable for a main control chip, and the main control chip communicates with the plug-in chip through an SDIO interface. Wherein, a register (referred to as a signal mapping register) accessible by the SDIO interface is pre-configured in the RFU partition of the external chip, and the signal mapping register is configured to map signals corresponding to the DAP integrated in the external chip.

[0050] In this embodiment, the external chip may be, for example, an ARM chip, and the ARM chip usually integrates a SWD interface as its DAP port. The SWD interface realizes the debugging of the ARM chip through a data line and a clock line, and its corresponding signals include data signals and clock signals.

[0051] On this basis, the signal mapping register is configured to map the data signal and clock signal of the DAP port. Specifically, four bits (bits) of the signal map...

Embodiment 3

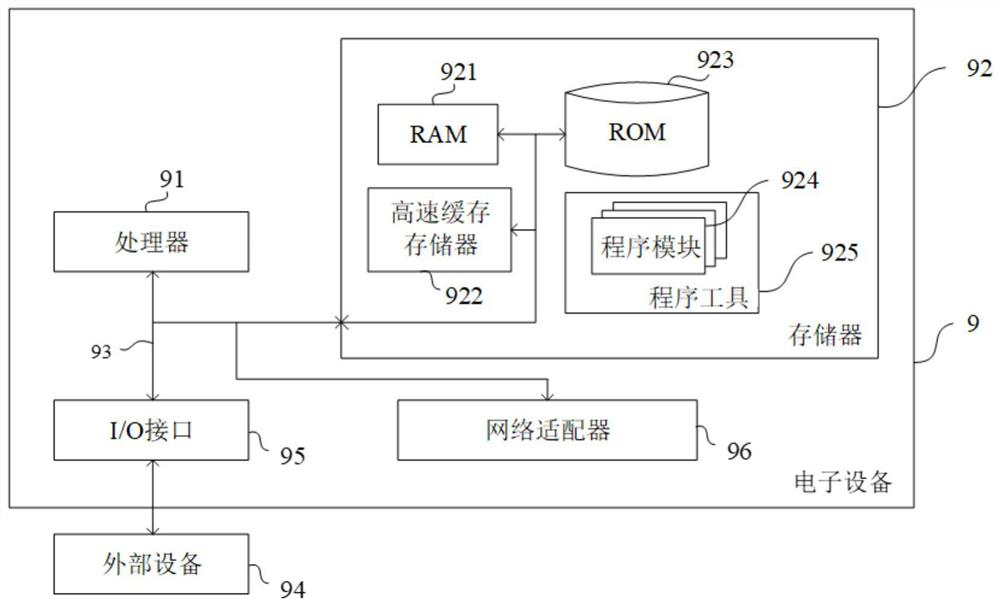

[0064] This embodiment provides an electronic device, which can be expressed in the form of a computing device (for example, it can be a server device), including a memory, a processor, and a computer program stored on the memory and operable on the processor, wherein the processor The steps of the method for debugging an external chip through the SDIO interface provided in Embodiment 1 can be implemented when the computer program is executed.

[0065] image 3 A schematic diagram of the hardware structure of this embodiment is shown, as image 3 As shown, the electronic device 9 specifically includes:

[0066] At least one processor 91, at least one memory 92, and a bus 93 for connecting different system components, including the processor 91 and the memory 92, wherein:

[0067] The bus 93 includes a data bus, an address bus, and a control bus.

[0068] The memory 92 includes a volatile memory, such as a random access memory (RAM) 921 and / or a cache memory 922 , and may fu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com