NAND memory and manufacturing method thereof

A manufacturing method and memory technology, applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve problems affecting the normal use of devices, affecting the connection of metal contact holes, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

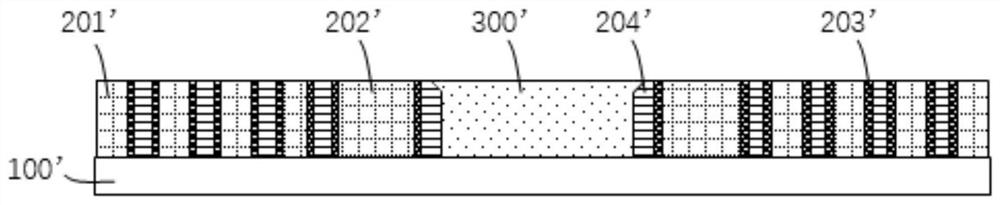

[0051] In the manufacturing method of the above-mentioned NAND memory, when the first sidewall 204' is etched, the first sidewall 204' between the selection tube 202' and the interlayer dielectric layer 300' is removed, resulting in subsequent When the air gap between the word lines 201' is formed, a void A appears in the interlayer dielectric layer 300' (ie Figure 1EIn the area indicated by A). Since the contact hole made in the subsequent manufacturing process of the NAND memory needs to pass through the interlayer dielectric layer 300' and be filled with metal, the existence of the void A will cause the connection between the contact hole and the contact hole, thereby affecting the normal use of the device.

[0052] In order to avoid the above situation, this embodiment provides a method for manufacturing a NAND memory, figure 2 It is a flow chart of the manufacturing method of the NAND memory provided by this embodiment. refer to figure 2 It can be seen that the manu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com