High-density trench device structure and manufacturing method thereof

A technology of device structure and manufacturing method, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as limiting cell size, simplify the overall structure, increase cell density, and reduce device characteristic conduction The effect of resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

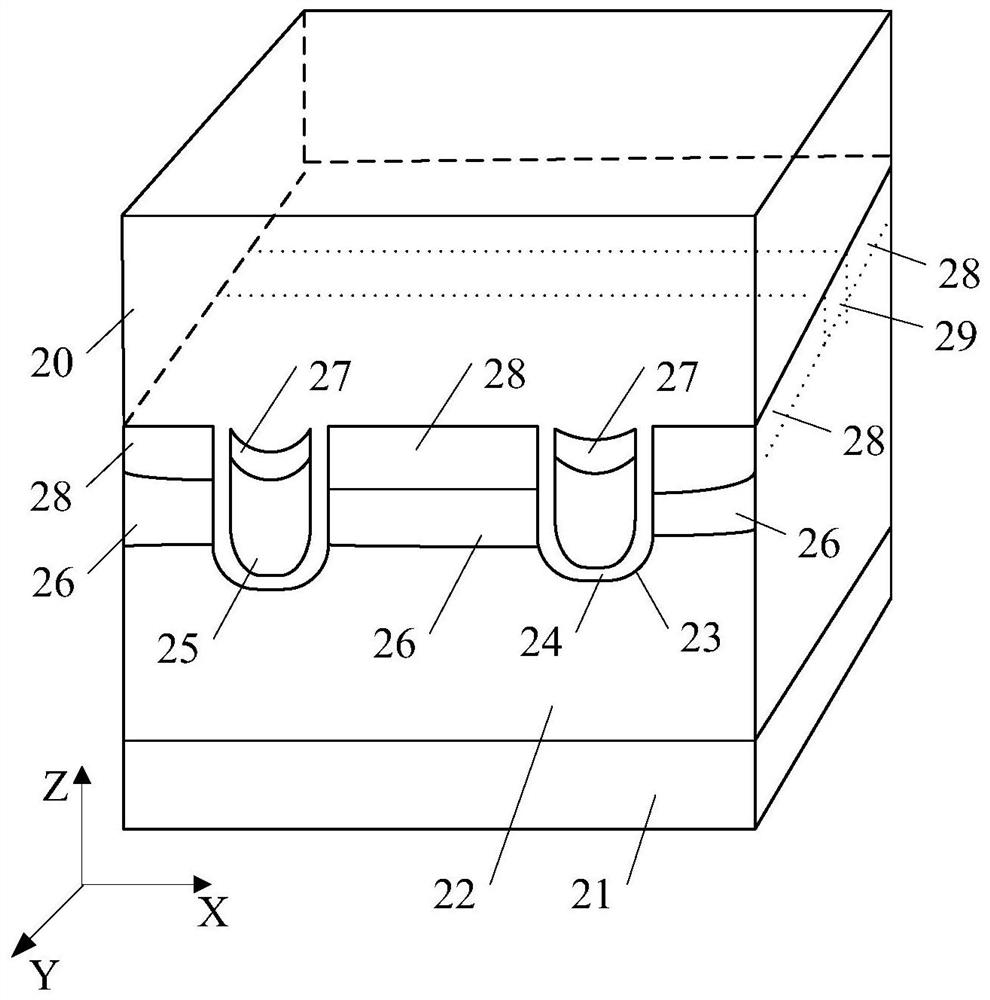

[0053] refer to figure 1 , Figure 3A-Figure 3H As shown, this embodiment provides a high-density trench device structure, including: a substrate 21 of the first conductivity type;

[0054] An epitaxial layer 22 of the first conductivity type located above the substrate 21;

[0055] a plurality of source regions of the first conductivity type formed along the X-axis direction and located above the base region at intervals in the Y-axis direction;

[0056] a base region 26 located above the epitaxial layer 22 and having a second conductivity type;

[0057] Also includes:

[0058] The trench 23 is also lined with an isolation layer 27, and the isolation layer 27 is located above the gate 25;

[0059] A plurality of source regions 28 of the first conductivity type located above the base region 26 are distributed at intervals along the X-axis direction;

[0060] a second conductivity type source region 29 located above the base region 26 and in a spacer region of the first con...

Embodiment 2

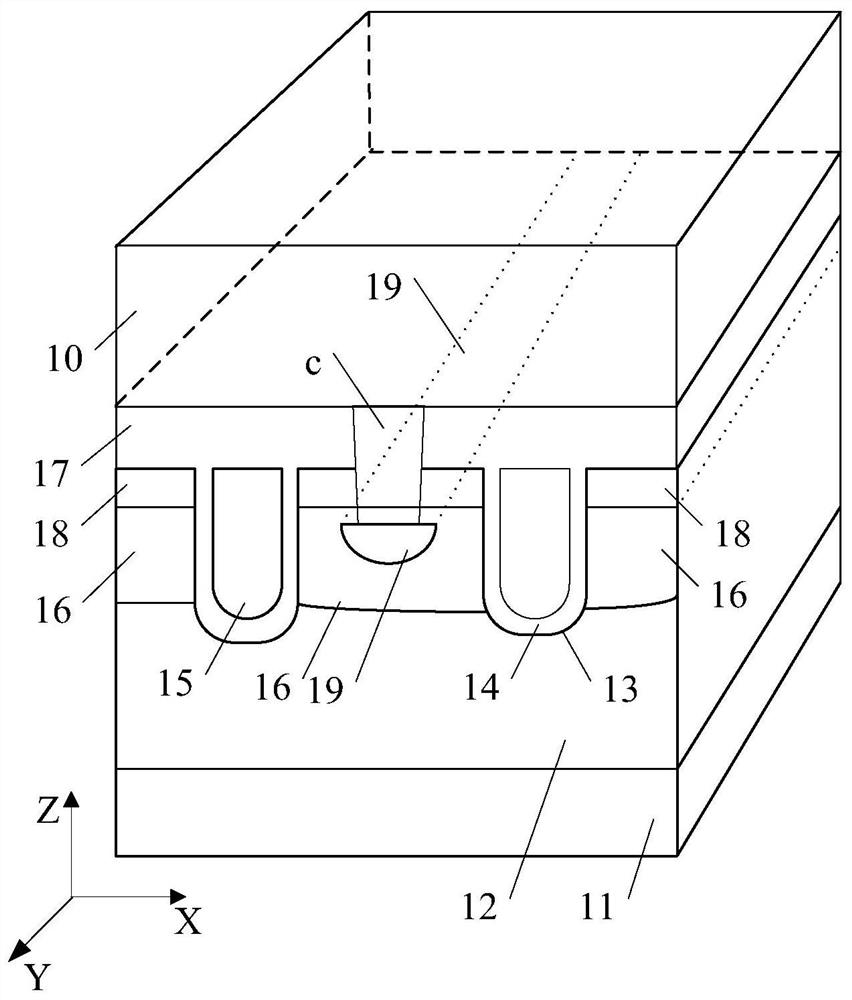

[0076] refer to figure 1 , Figure 3A-Figure 3H As shown, among them, Figure 3A-Figure 3H The manufacturing method and process of the high-density trench device structure of this embodiment will be described. This embodiment provides a method for manufacturing a high-density trench device structure, including:

[0077] S1. Form the epitaxial layer 22 of the first conductivity type on the substrate 21 of the first conductivity type (see Figure 3A );

[0078] Wherein, the thickness of the epitaxial layer 22 is 1um˜5um. In practical applications, the thickness of the epitaxial layer 22 can be set according to the withstand voltage requirements of the device.

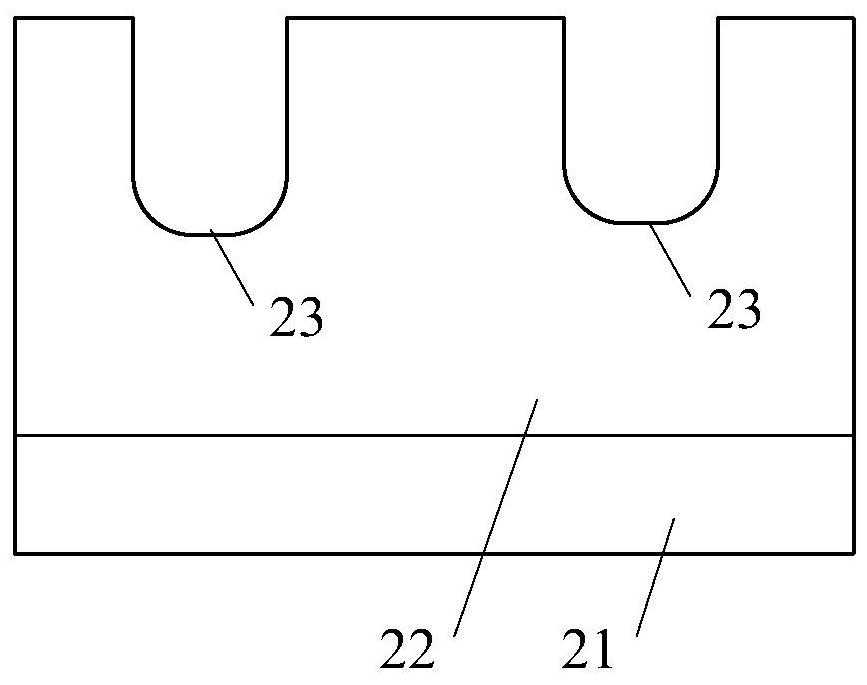

[0079] S2. Etching trenches 23 in the epitaxial layer 22 along the Y-axis direction (see Figure 3A );

[0080] Specifically, the groove 23 is etched along the Y-axis direction on the epitaxial layer 22 , the etching depth of the groove 23 is 1 um-2 um, the width is 0.2 um-0.7 um, and the groove distance is greate...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Depth | aaaaa | aaaaa |

| Width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com