SRAM storage device and method based on SRIO protocol

A storage device and protocol technology, applied in the direction of information storage, static memory, digital memory information, etc., can solve the problems of SRAM storage volume expansion, storage volume cannot expand the refresh time, etc., and achieve the effect of capacity expansion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

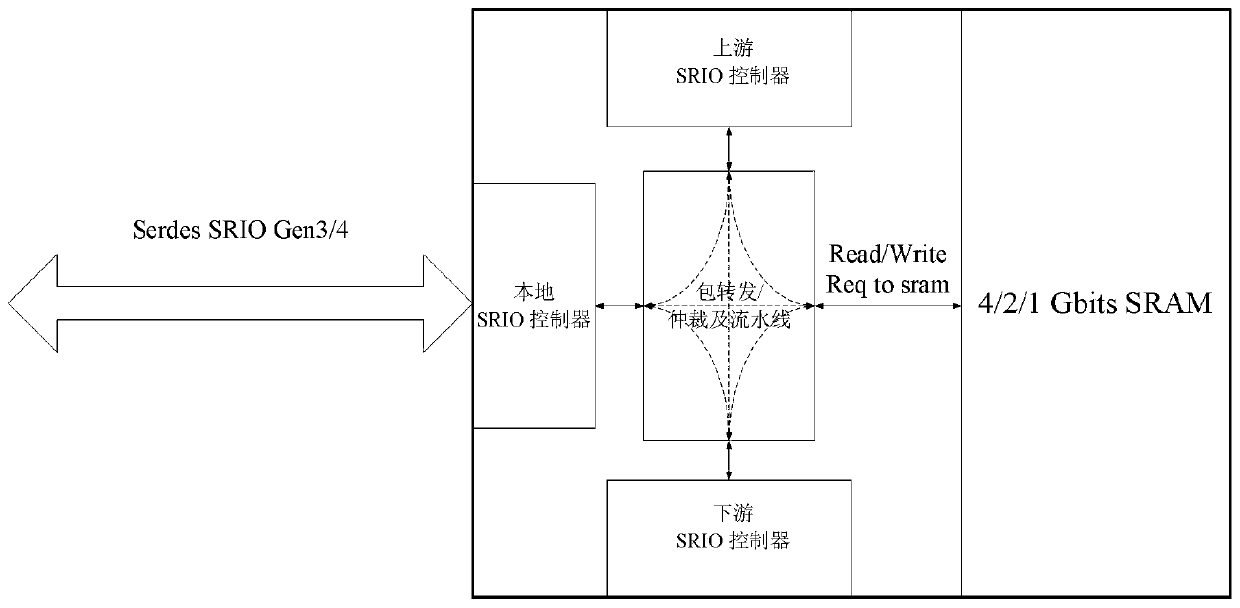

[0033] Such as figure 1 As shown, an SRAM storage device based on the SRIO protocol includes an SRAM storage bank, an SRIO controller, a packet forwarding logic module, an arbitration logic module, and a pipeline logic module.

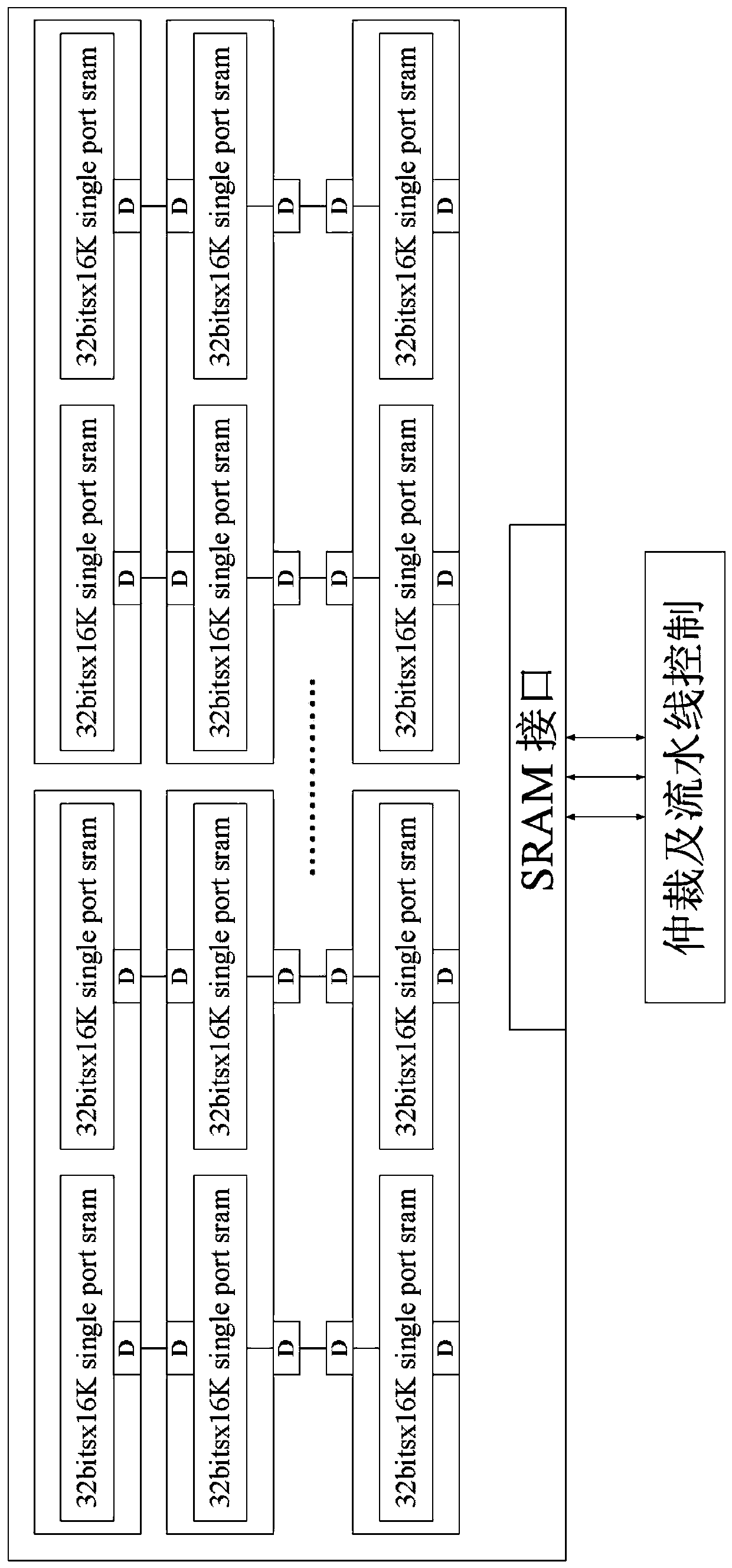

[0034] The SRAM memory bank is 4Gbits or 2Gbits or 1Gbits SRAM; 4Gbits or 2Gbits or 1Gbits SRAM is designed to be spliced by a plurality of small single-port SRAMs according to the address, because the small SRAM is convenient for back-end physical design and implementation. Taking the SRAM with a data bit width of 32bits and a depth of 16K as an example, 8192, 4096 and 2048 banks are required to form 4Gbits, 2Gbits and 1Gbits SRAM banks respectively. Such as figure 2As shown, a 1Gbits SRAM memory bank requires a total of 2048 single-port SRAMs with a 32bits width and a 16K depth to be spliced according to addresses. According to the physical implementation of the backend, the multi-level registers in the pipeline are respectively placed between...

Embodiment 2

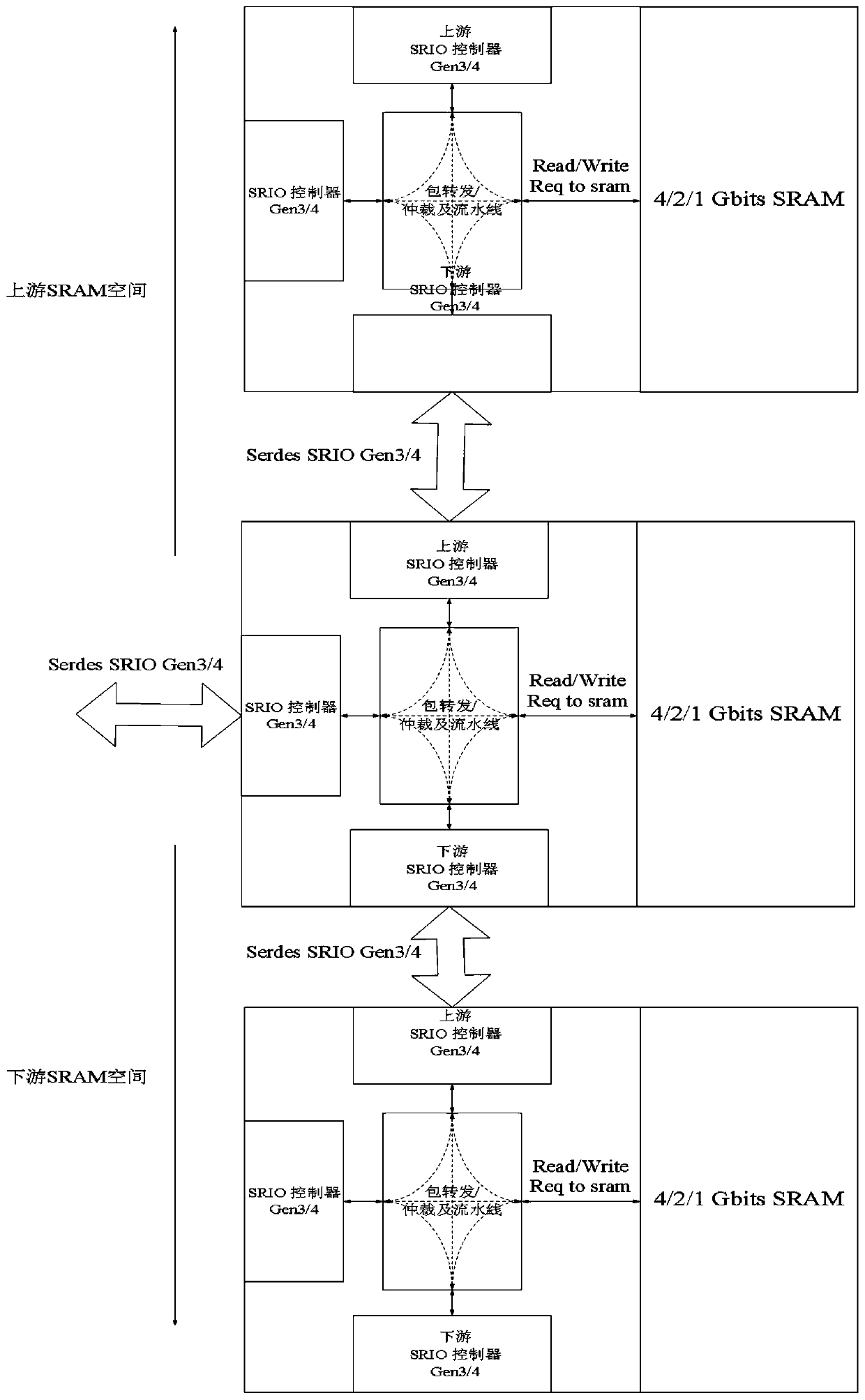

[0043] Such as Figure 7 As shown, based on the SRAM storage device based on the SRIO protocol provided in Embodiment 1 of the present invention, Embodiment 2 of the present invention also provides an SRAM storage method based on the SRIO protocol, the method comprising:

[0044] Step S1: the local SRIO controller inputs a read and write request to the SRAM memory bank, and outputs the read and write request packet to the packet forwarding logic module through the first register;

[0045] Step S2: The packet forwarding logic module judges which one of the target of the request is the local SRAM space, the upstream SRAM space or the downstream SRAM space according to the address in the read and write request packet, and forwards and reads according to the target of the request The request packet, the forwarded read and write request packet passes through the second register and is output to the arbitration logic module;

[0046] Step S3: The arbitration logic module selects mu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com