Multi-core processor

A multi-core processor, processor technology, applied in electrical digital data processing, instruments, data transformation and other directions, can solve the problem of sacrificing hard real-time performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] In order to make the purpose, technical solution and advantages of the present application clearer, the technical solution of the present application will be described in detail below. Apparently, the described embodiments are only some of the embodiments of this application, not all of them. Based on the embodiments in the present application, all other implementation manners obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present application.

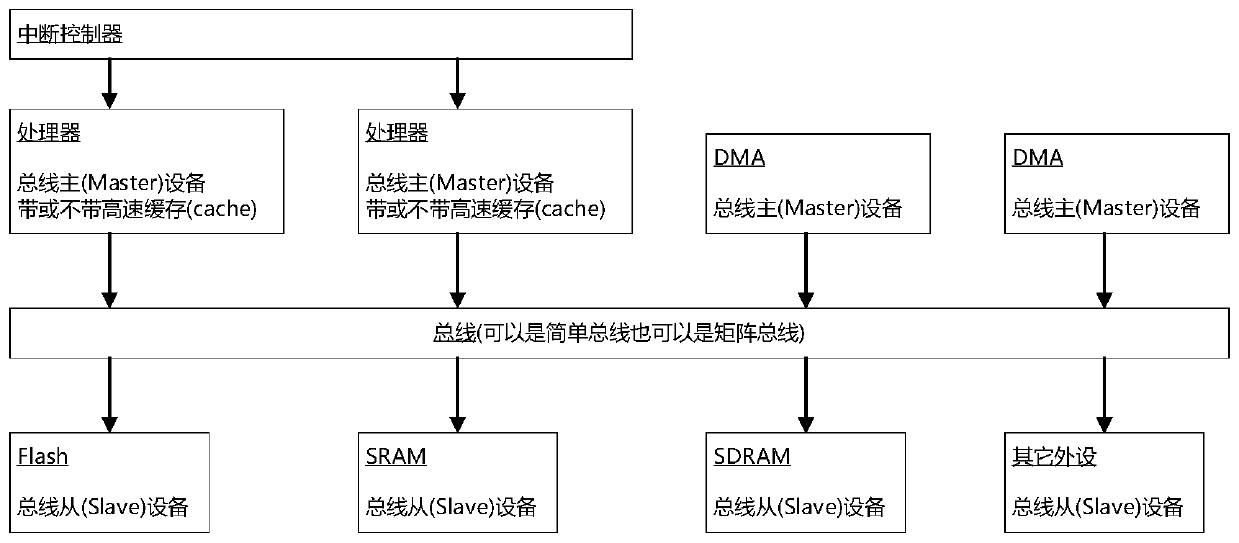

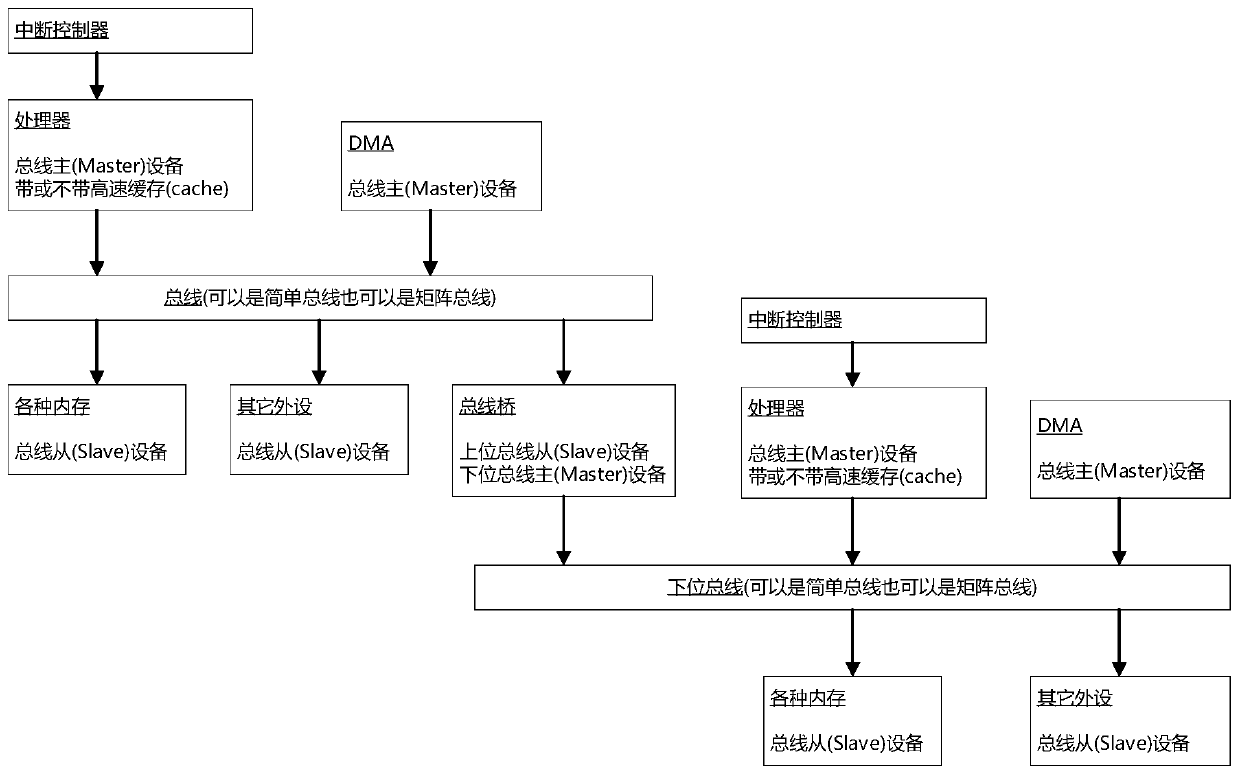

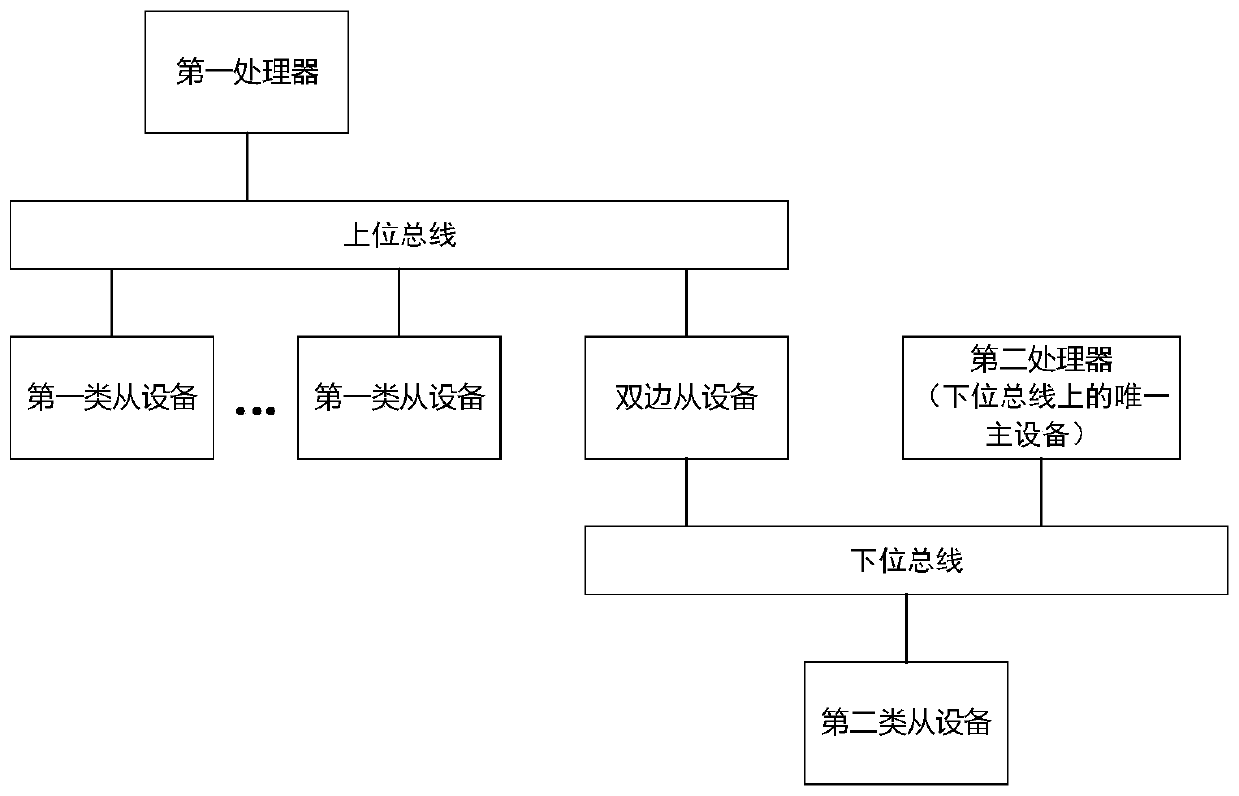

[0033] Since the current multi-core processors are provided with multiple bus masters on the bus in order to make full use of the bandwidth, etc., the real-time performance is reduced, which is not conducive to the timely completion of services with high real-time performance requirements. Therefore, the embodiment of the present application provides a multi-core processor, which ensures its real-time performance without affecting efficiency and bandwidth utiliza...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com