FPGA-based SOC chip automatic test tool and test method

A technology of automated testing and testing tools, applied in the direction of electronic circuit testing, measuring electricity, measuring devices, etc., can solve the problems of cumbersome communication at various baud rates, repeated work, cumbersome plugging and unplugging of connecting wires, etc., to achieve automated testing Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

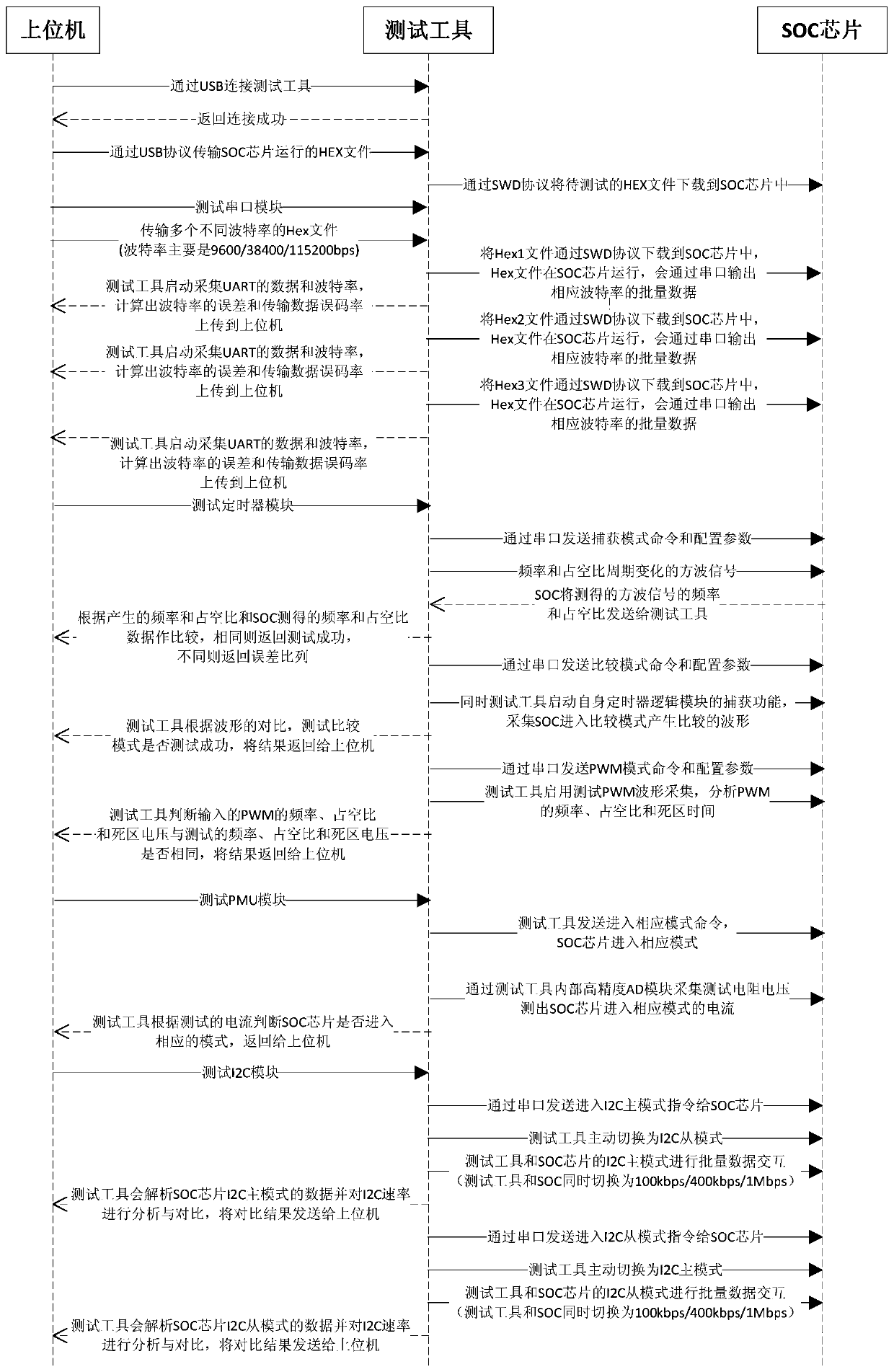

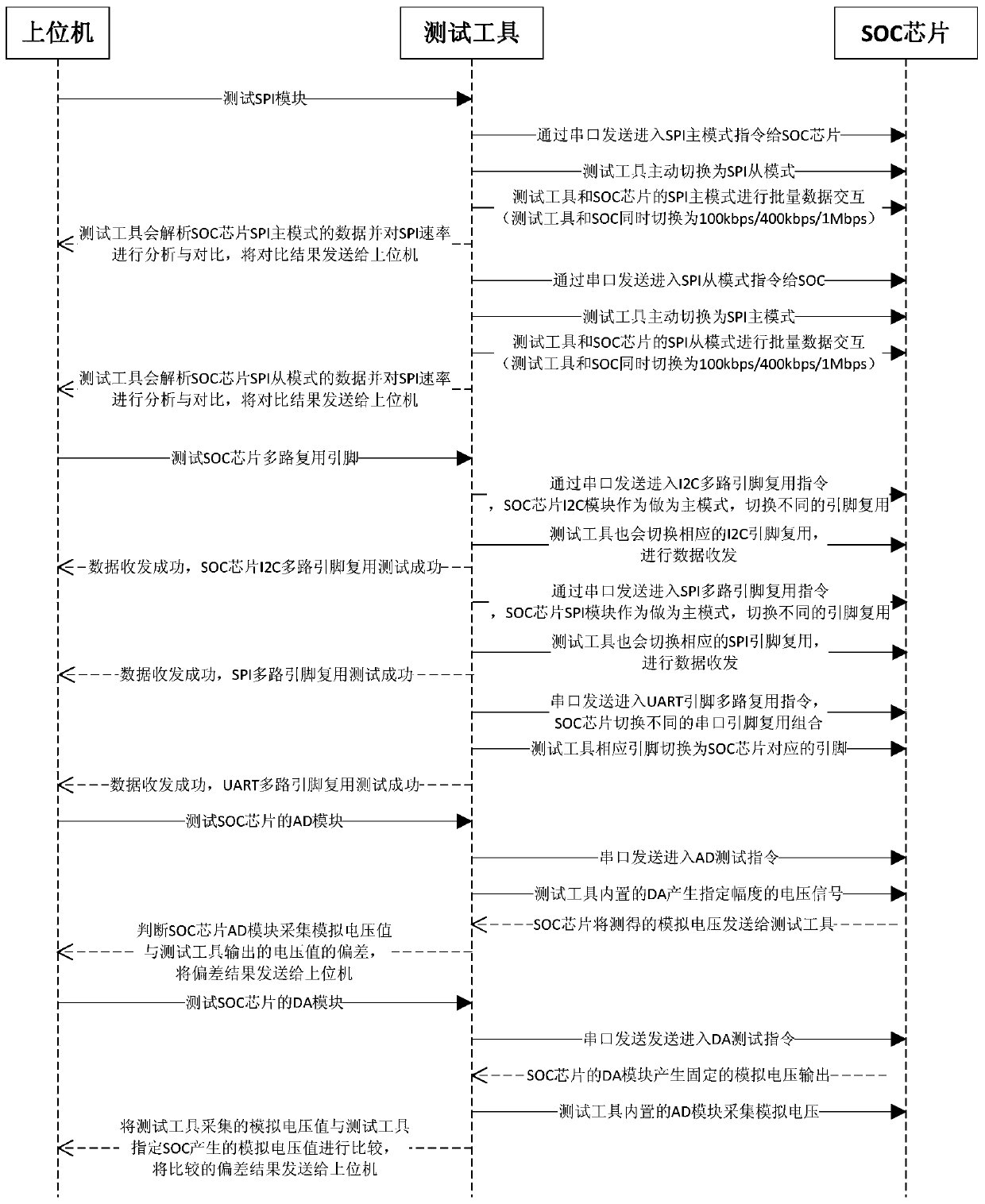

[0047] The present invention will be further described below in conjunction with specific drawings and embodiments.

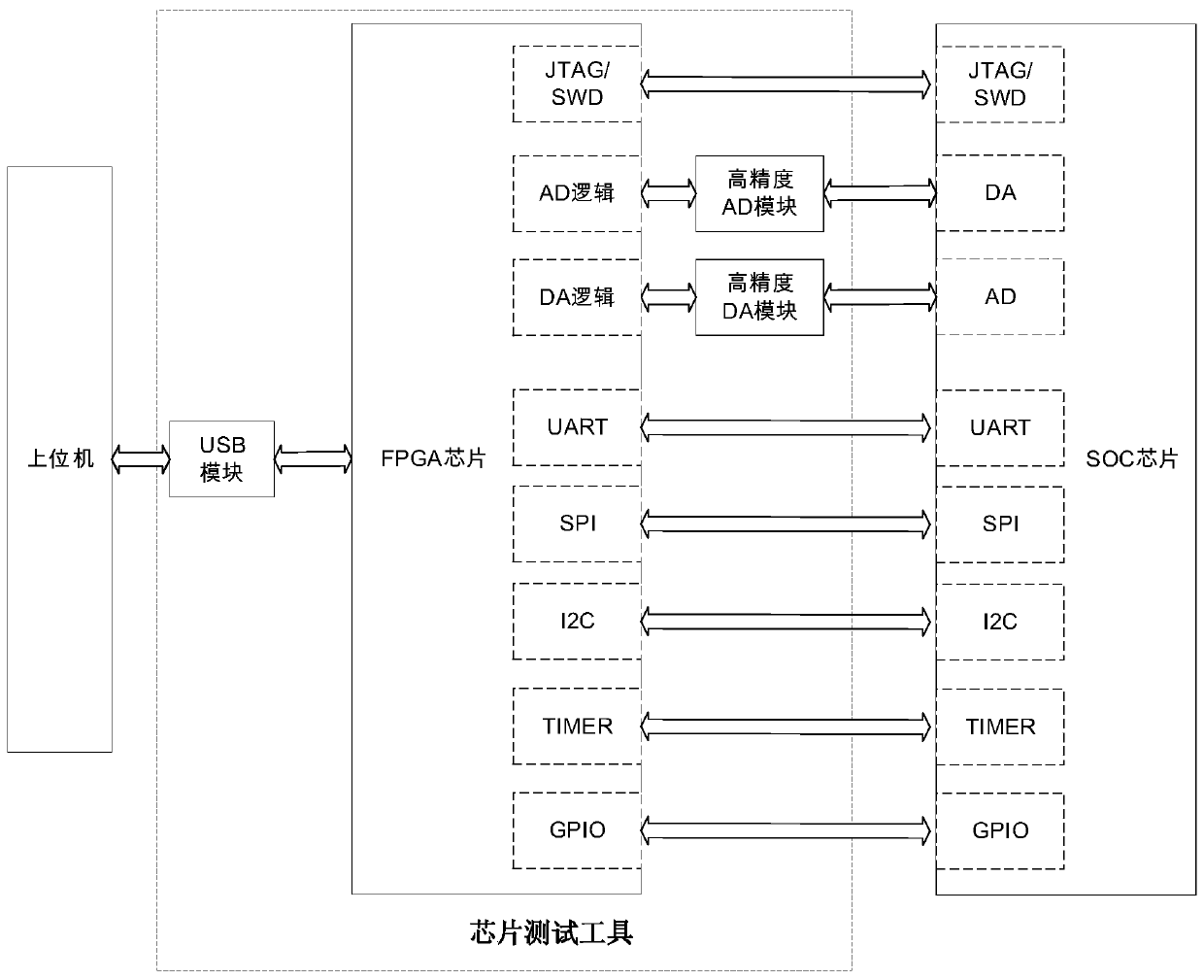

[0048] The embodiment of the present invention proposes an FPGA-based SOC chip automated testing tool, including a connected host computer interface module, an FPGA chip, a high-precision AD module, and a high-precision DA module; the host computer interface module is used to connect the host computer, Specifically, the USB module is used;

[0049] The FPGA chip is provided with:

[0050] The JTAG / SWD logic module is used to connect the JTAG / SWD module on the SOC chip;

[0051] AD logic module, which controls the high-precision AD module to connect with the DA module on the SOC chip;

[0052] DA logic module, which controls the high-precision DA module to connect with the AD module on the SOC chip;

[0053] UART logic serial port module, used to connect to the UART serial port module on the SOC chip;

[0054] The SPI logic module is used to connect the SPI ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com