N-M AXI bus controller and configurable arbitration mechanism implementation method thereof

An N-MAXI, bus controller technology, applied in the direction of instruments, electrical digital data processing, etc., can solve the problem of the inability to achieve flexible priority configuration of multiple SLAVE slave devices, and the inability to achieve flexible priority configuration of multiple MASTER master devices. Flexibility, efficiency and other issues, to achieve the effect of design reusability, simplifying design complexity, and reducing design difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

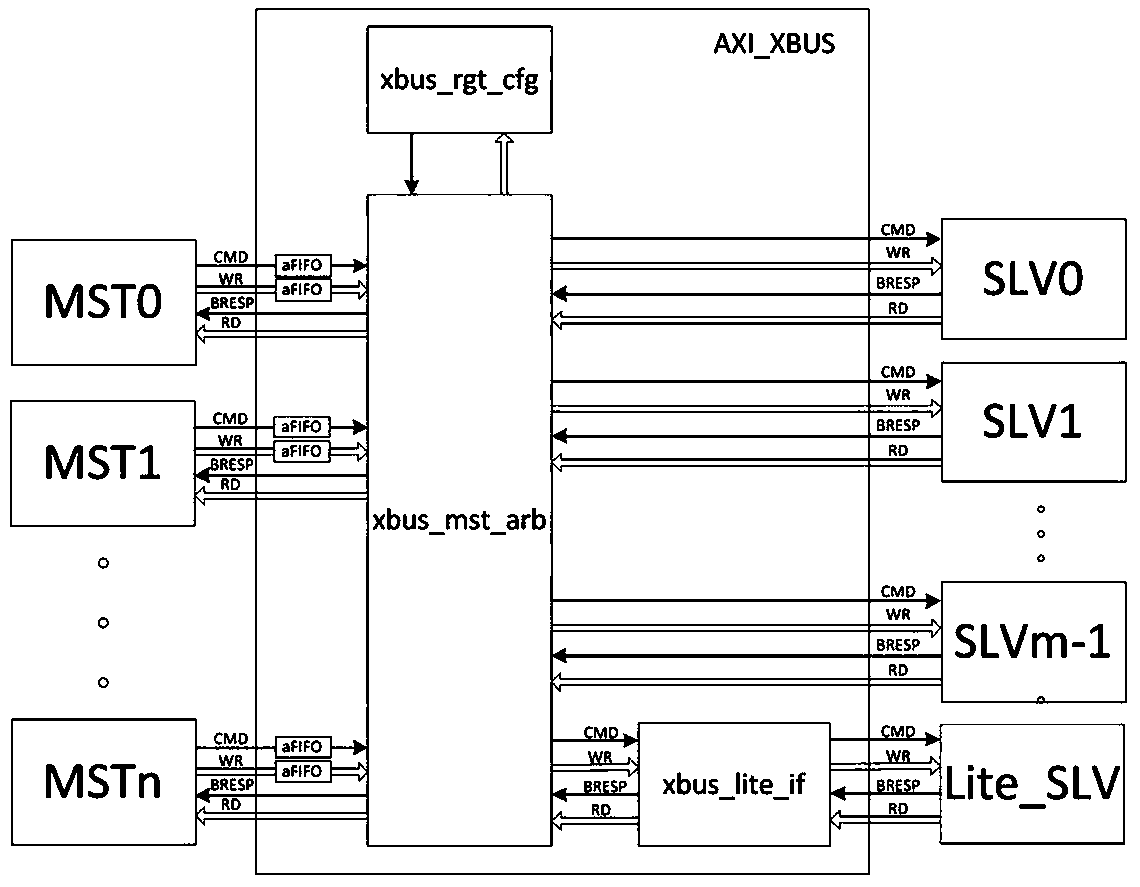

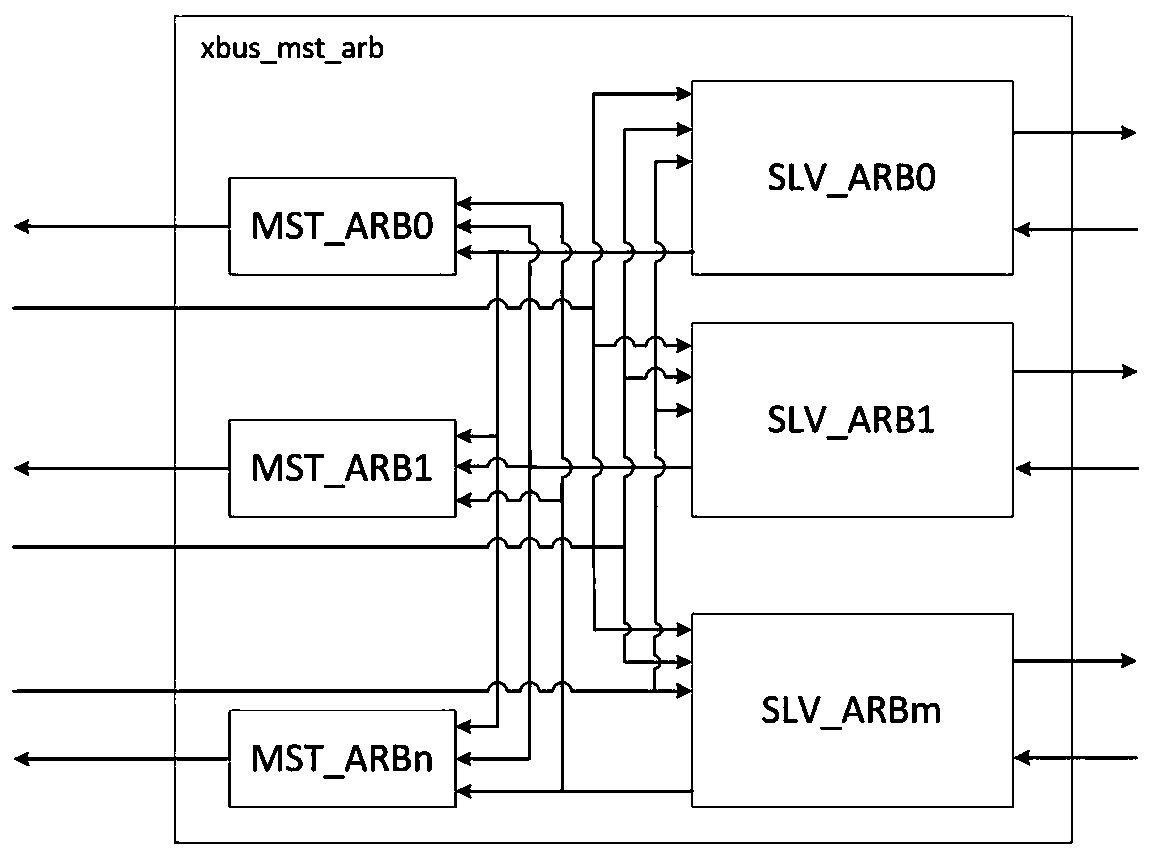

[0023] This embodiment discloses a N-M AXI bus controller based on a configurable arbitration mechanism, such as figure 1 As shown, xbus_rgt_cfg module, xbus_lite_if module and xbus_mst_arb module. xbus_rgt_cfg is the internal configuration module of the bus control, which exists as a generalized SLAVE in the bus controller, and the external master controls the functional characteristics of the bus controller through this module, and the arbitration priority vector of each master-slave device implemented in the present invention That is, after configuring this module, it is exported to the full interconnection; xbus_lite_if is responsible for converting slave instructions and data into lite mode, used to connect with lite_slv, and only used when connecting to lite slave; xbus_mst_arb is an N-M full interconnection implementation module, responsible for arbitration The command of the external master is authorized to the corresponding master through punching, and the command is ...

Embodiment 2

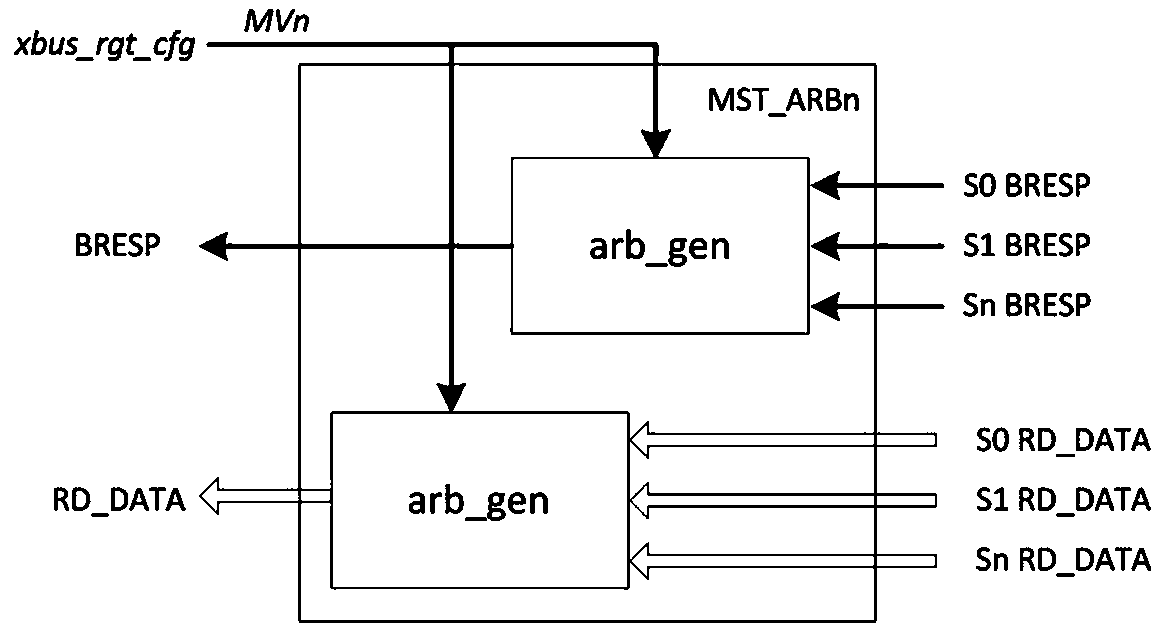

[0031] This embodiment discloses a method for realizing a configurable arbitration mechanism of an N-M AXI bus controller. In this method, N masters and M slaves connected to the AXI bus controller are all configured with arbitration priority vectors, and all arbitration priority vectors All can be configured independently, the arbitration priority vector of each slave is used for the arbitration of the read command channel and the write command channel, in which the write data channel is attached to the write command channel, and the arbitration priority vector of each master is used for reading data Arbitration of channels and write response channels.

[0032] In this embodiment, for the read command channel, the write command channel, the read data channel and the write response channel, the signals participating in the arbitration are respectively the empty and full signals of the FIFOs on the corresponding channels. Specifically, the arbitration participation signal on th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com