Port connection method and system for improving verification environment reusability and medium

A technology for verifying the environment and connection method, applied in the direction of functional inspection, detection of faulty computer hardware, instruments, etc., can solve the problems of non-reusability, error-prone, reducing verification efficiency, etc., to avoid artificial introduction of errors and save verification workload. , the effect of improving the verification efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

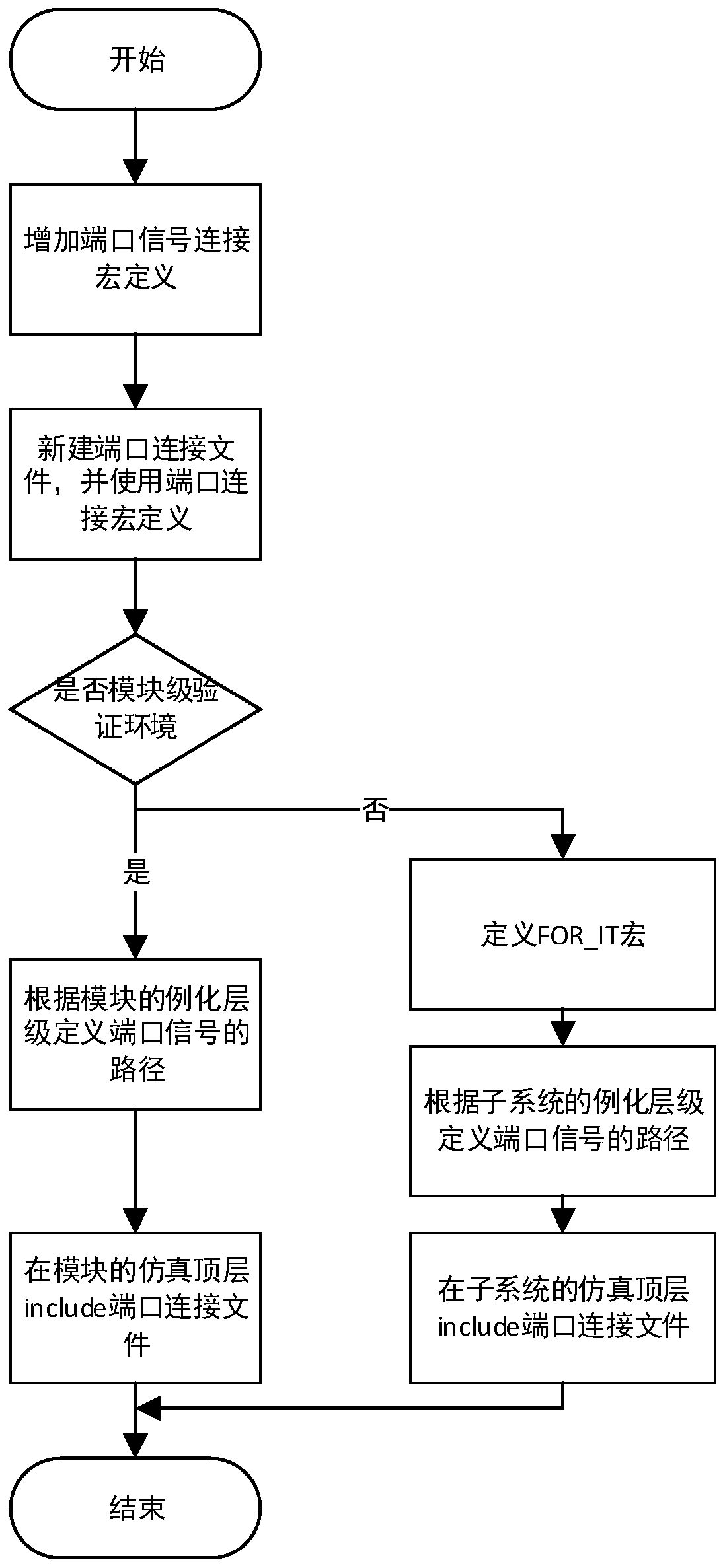

[0040] The technical solution will be described in detail below through a preferred embodiment and in conjunction with the accompanying drawings.

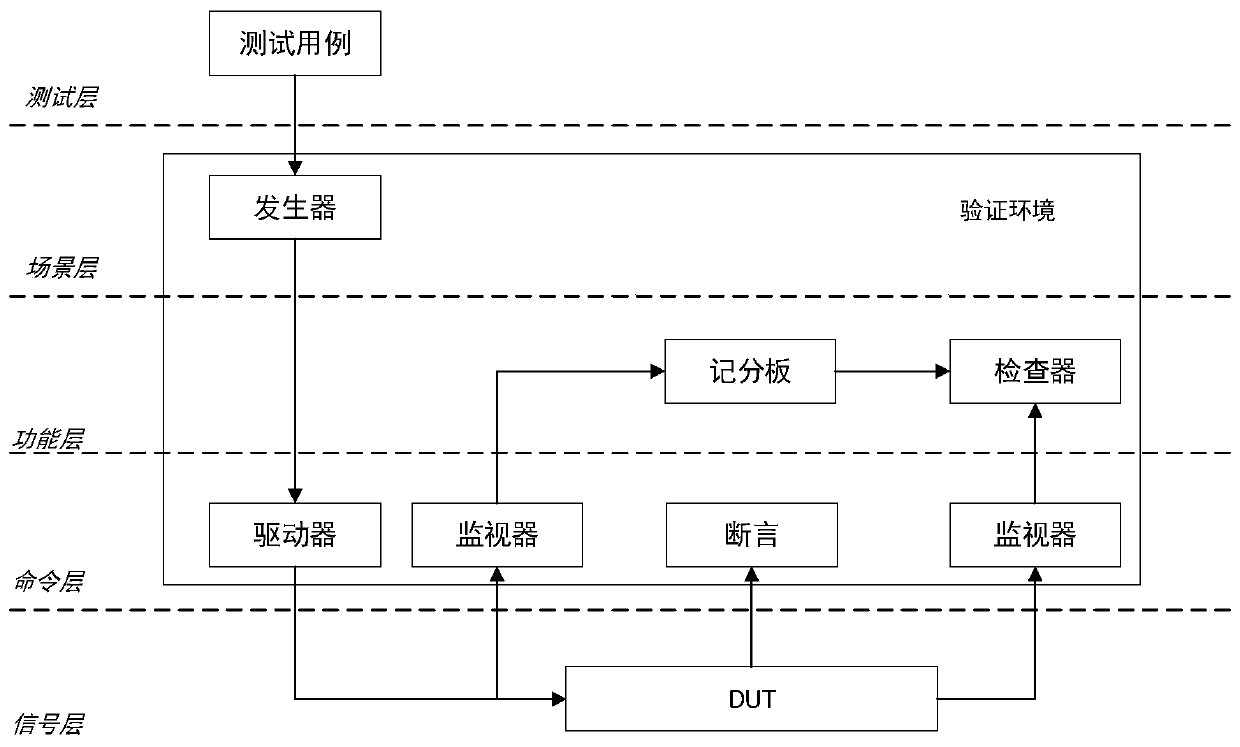

[0041] A verification system that improves the reusability of the verification environment can be referred to figure 1 Prior art, including DUT and verification environment, described verification environment includes command layer and function layer, set signal layer, command layer, function layer, scene layer and test layer sequentially from bottom to top, wherein verification environment includes generator, agent , drivers, monitors, inspectors, scoreboards, and assertions. Generators, Drivers, Monitors, Checkers, Scoreboards, and Assertions are each verification components.

[0042] This embodiment focuses on the signal layer, the command layer and the functional layer;

[0043] The signal layer includes DUT and interface;

[0044] The command layer is above the signal layer, and is used to connect downward with the DUT thro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com