A device and method for reducing adc sampling rate

A sampling rate, band-pass sampling technology, applied in the field of terahertz communication, achieves the effects of easy implementation, small structural restrictions, and simplified circuit design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

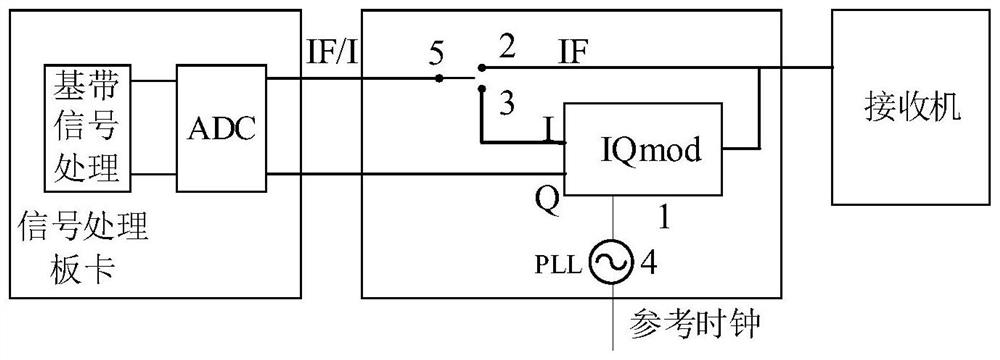

[0030] Such as Figure 1-2 As shown, this embodiment provides a technical solution: a device for reducing the ADC sampling rate, including an IQ modulator 1, a single-pole double-throw switch 5, an intermediate frequency band-pass sampling link 2, a PLL reference clock configurator 4, and a zero-IF Sampling link 3;

[0031] The intermediate frequency bandpass sampling link 2 and the zero intermediate frequency sampling link 3 are set in parallel;

[0032] The SPDT switch 5 is used to control the opening and closing of the intermediate frequency bandpass sampling link 2 and the zero intermediate frequency sampling link 3, and select different sampling modes;

[0033] The PLL reference clock configurator 4 is electrically connected to the IQ modulator 1 for generating a clock pulse signal;

[0034] The IQ modulator 1 is located in the zero-IF sampling link 3 and is used to demodulate the IF signal processed by the receiver.

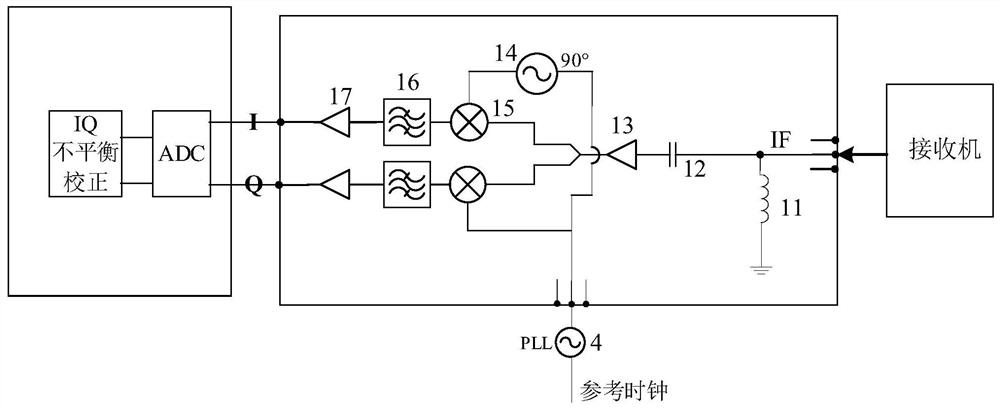

[0035] The IQ modulator 1 includes an inductor 11,...

Embodiment 2

[0048] The difference between this embodiment and Embodiment 1 is that this embodiment provides a method for reducing the ADC sampling rate, including the following steps:

[0049] S1: The receiver down-converts the terahertz signal to an intermediate frequency signal

[0050] The signal is down-converted from the terahertz signal THz in the receiver to become the intermediate frequency signal IF;

[0051] S2: Select the sampling link through the single-pole double-throw switch 5 according to the center frequency of the signal.

[0052] When the signal center frequency of the intermediate frequency signal IF in S1 is relatively high, the intermediate frequency band-pass sampling link 2 is turned on through the SPDT switch 5;

[0053] S3: Sampling and processing the signal through the sampling link selected in S2

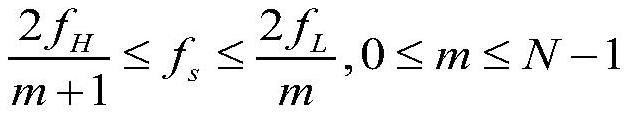

[0054] When the intermediate frequency band-pass sampling link 2 is turned on, the intermediate frequency signal IF with a higher center frequency is directly conn...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com