Segmented pseudo-data weighted average DEM circuit

A technology of weighted average and pseudo-data, which is applied in the field of segmented pseudo-data weighted average DEM circuit, can solve problems such as raising the noise floor, increasing modulator harmonics, increasing SFDR, etc., to suppress nonlinear energy and ensure linearity degree and eliminate nonlinear effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0051] The present invention will be described in further detail below in conjunction with specific examples, but the embodiments of the present invention are not limited thereto.

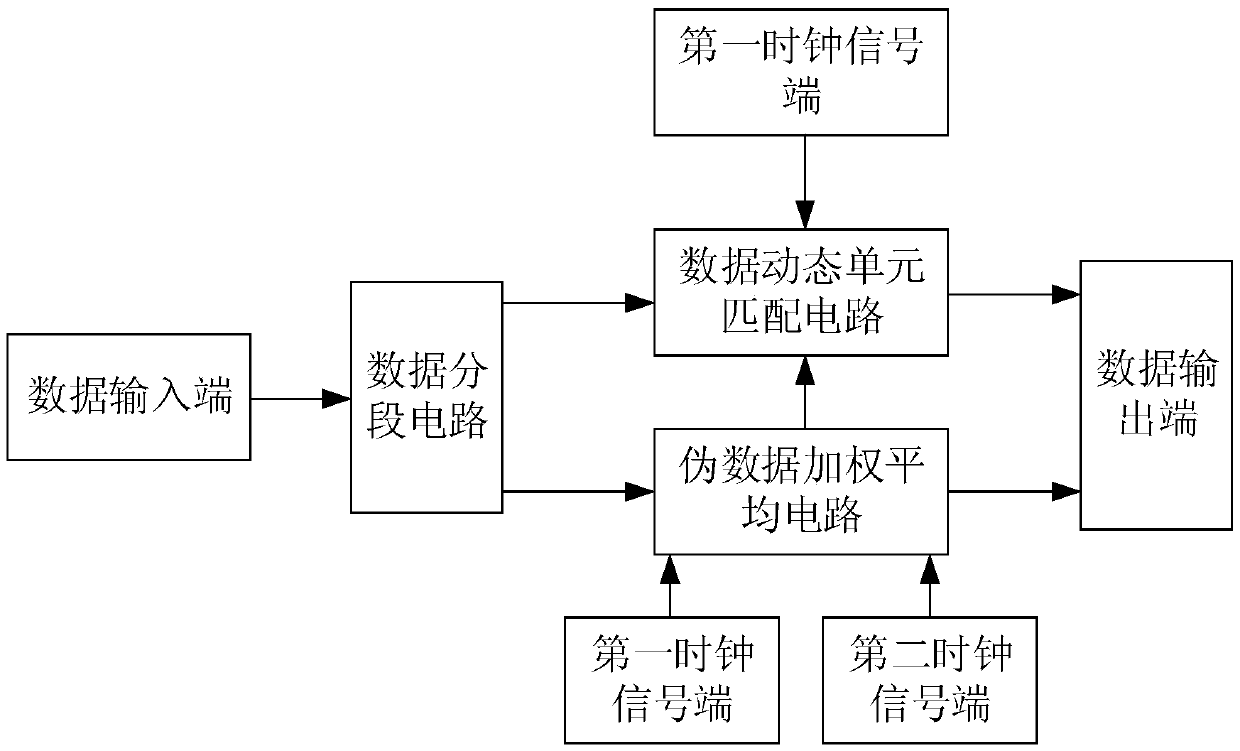

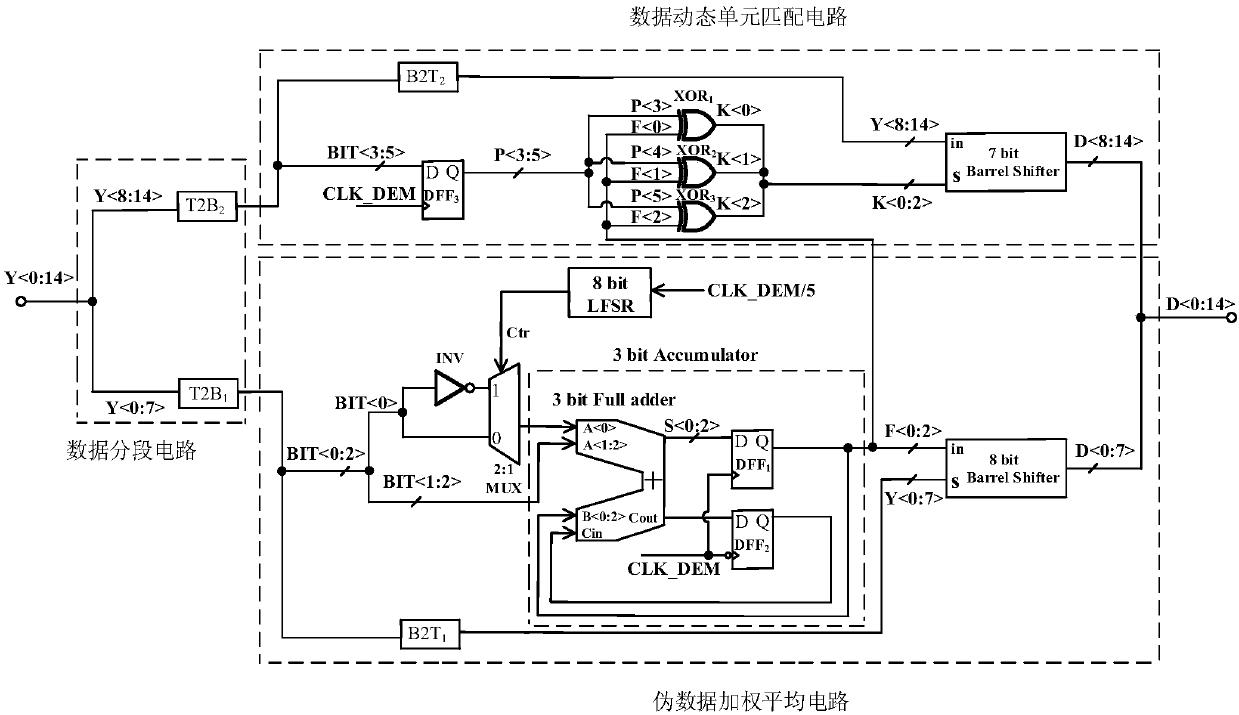

[0052] Seefigure 1 , figure 1 A schematic diagram of a circuit structure of a segmented dummy data weighted average DEM circuit provided by an embodiment of the present invention.

[0053] A segmented pseudo-data weighted average DEM circuit, comprising:

[0054] Data segmentation circuit, pseudo data weighted average circuit, data dynamic unit matching circuit, data input terminal, data output terminal, first clock signal terminal and second clock signal terminal;

[0055] a data segmentation circuit, configured to divide the input data into first data and second data;

[0056] A dummy data weighted average circuit, used to scramble the first data to obtain the third data and the pointer signal;

[0057] The data dynamic unit matching circuit is used to scramble the second data according to the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com