Multiple-bit comparator with reliable output timing and reduced hazards

A bit comparator and comparator technology, applied in the field of comparing multi-bit input signals, can solve problems such as timing design difficulties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

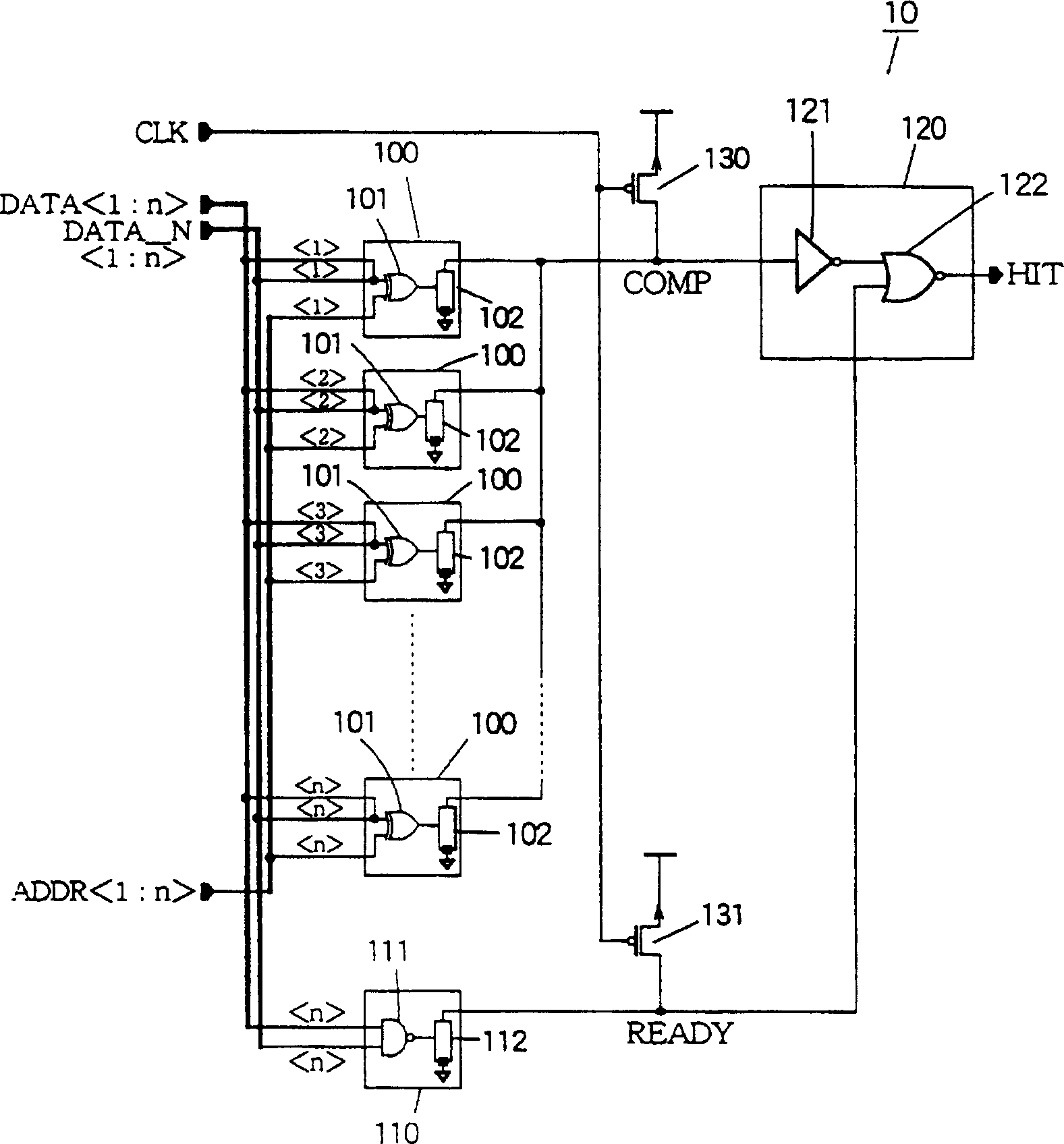

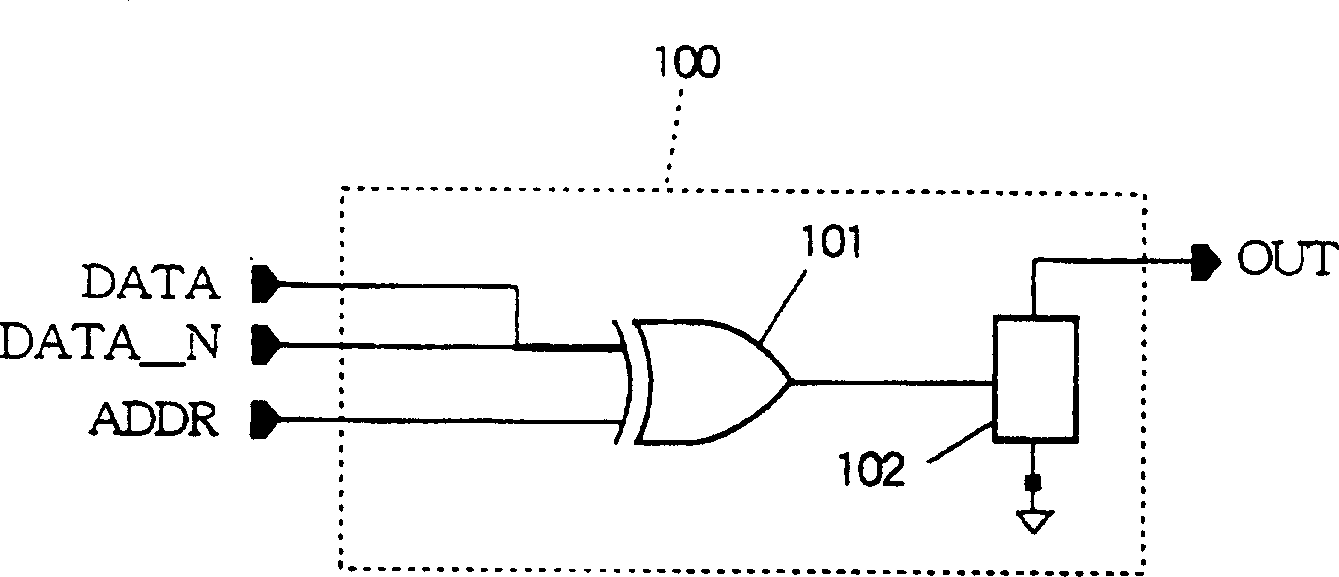

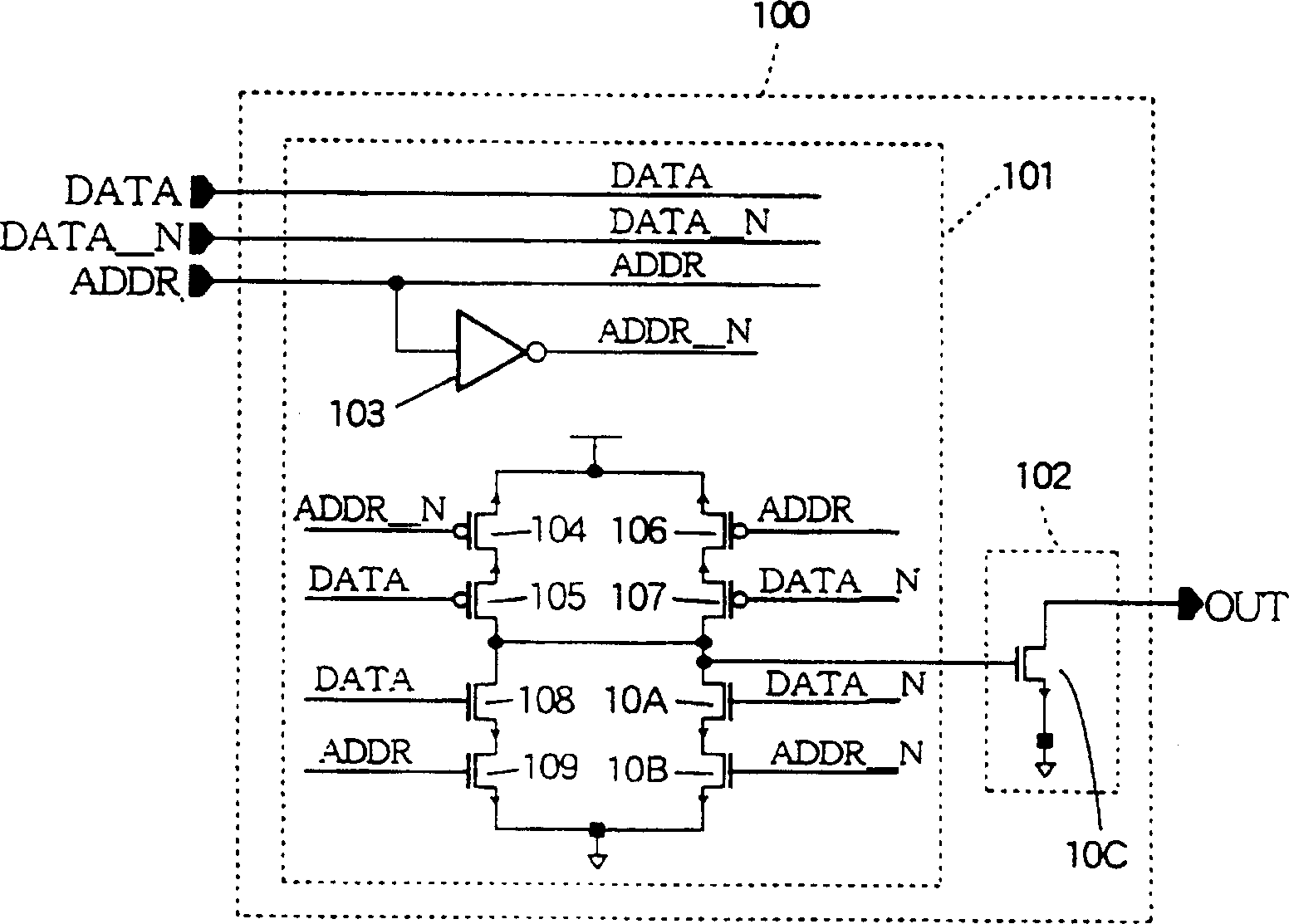

[0047] Embodiments of the present invention are described below with reference to the drawings. Although the embodiments are not limited to a particular manner of use, the embodiments will be described herein in connection with a cache memory in a semiconductor integrated circuit.

[0048] In the figure, the input signal to be compared is represented by ADDR and DATA. The notation indicates that each signal includes n bits input in parallel, and n is any integer greater than 1. Individual bits are marked to to identify. DATA is received in complementary form, and the complementary input is represented by DATA_N.

[0049] The input signals DATA, DATA_N, and ADDR are synchronized with a clock signal represented by CLK. The clock signal varies between a high level equal to the positive supply potential and a low level equal to zero potential or ground potential. These high and low levels are also the logic levels of the input signals DATA, DATA_N and ADDR. The power pot...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com