A bridging device for multi-way low speed peripheral integration

A bridging device and bridging technology, applied in the field of digital circuit front-end design, to achieve the effect of reducing the area of the circuit board, stable and reliable data transmission, and strong adaptability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] In order to make the purpose, content and advantages of the present invention clearer, the specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

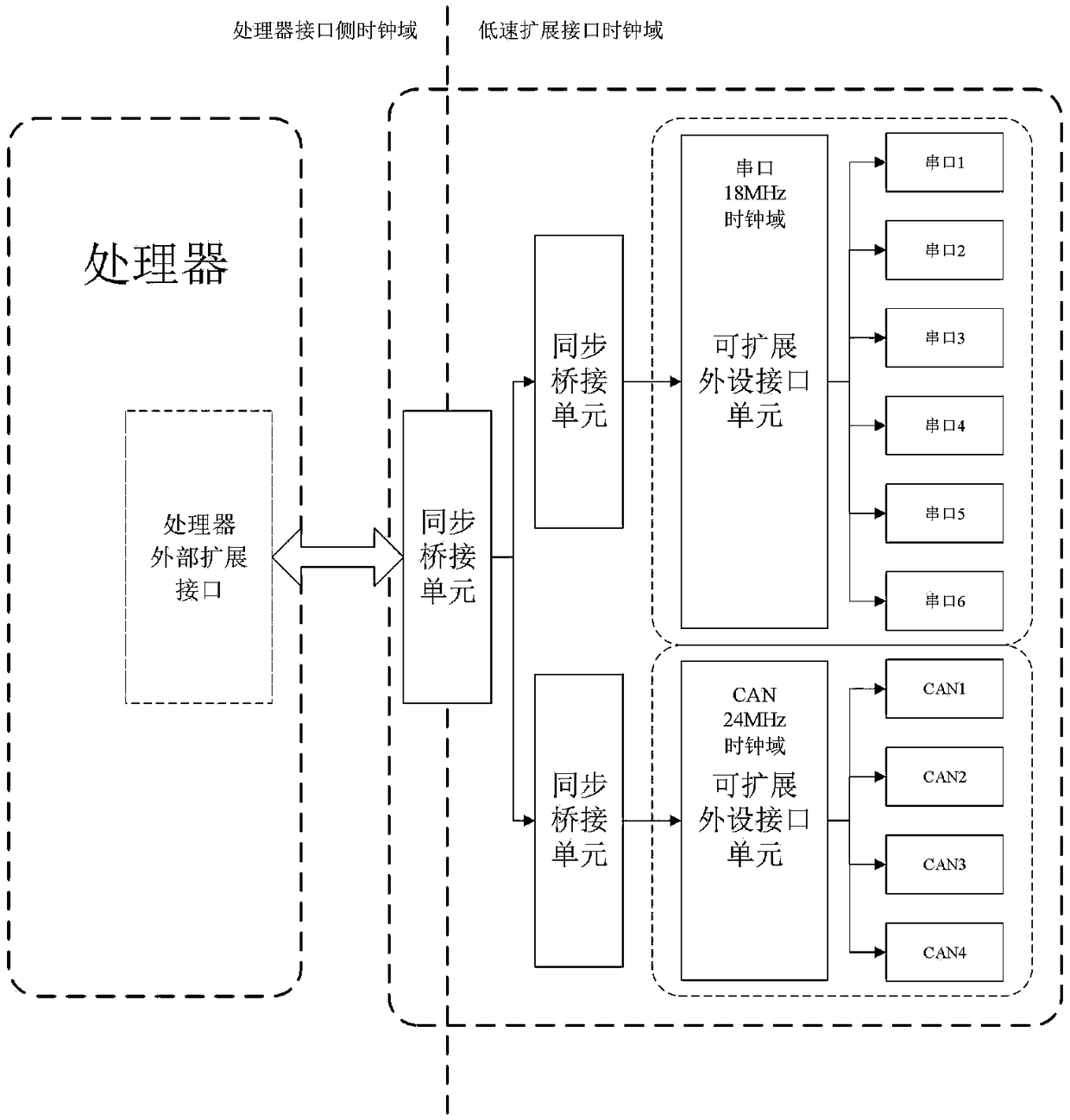

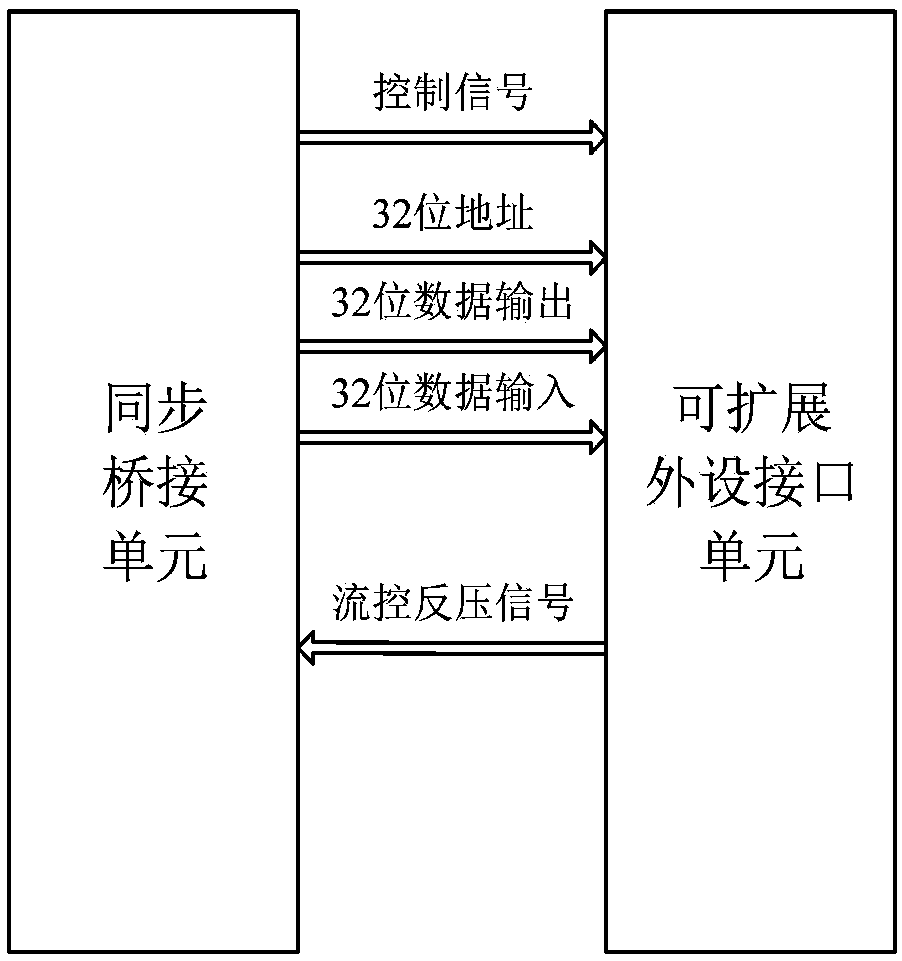

[0018] This embodiment proposes a bridge device for the integration of multiple low-speed peripherals that integrates six serial ports and four CAN controllers. Its architecture is as follows figure 1 shown. The bridge device includes a synchronous bridge unit and an expandable peripheral interface unit. Wherein, the synchronous bridge unit is a bidirectional interface unit, and the interface on one side realizes the connection with the external expansion interface of the processor; the interface on the other side realizes the connection with the extensible peripheral interface. The processor can use the synchronous expansion method, and use any clock within 100MHz to realize the interconnection with the synchronous br...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com