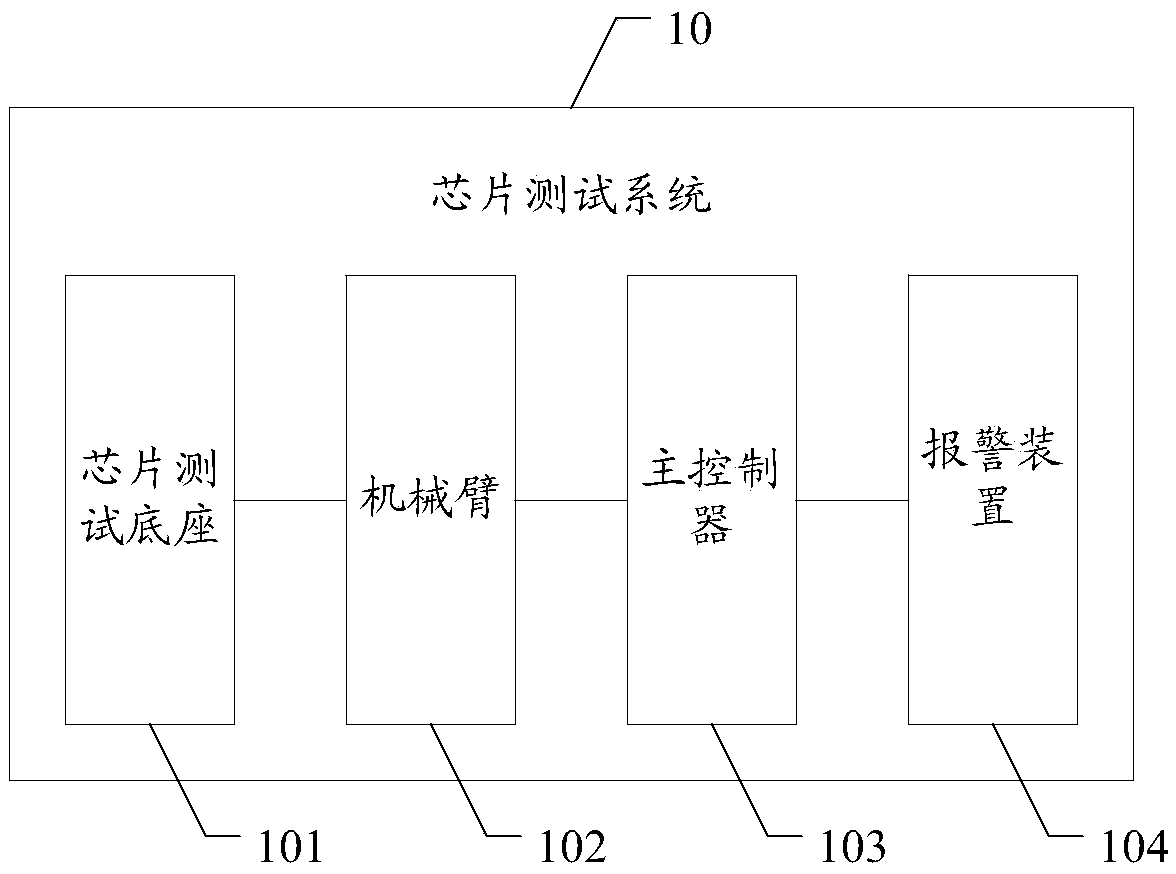

Chip test system

A chip testing and chip technology, which is applied in the direction of measuring devices, measuring electrical variables, measuring device casings, etc., can solve problems such as damage and unable to rule out chip test bases

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] In the prior art, after continuous test failures occur during the chip testing process, the test is usually stopped, and the specific reasons for the test failures are determined based on the experience of engineers, resulting in a longer cycle of chip testing.

[0024] In the embodiment of the present invention, an identification mark is set on the surface of the chip test base, and each time the robot arm places a chip on the chip test base, the identification sensor on the mechanical arm recognizes the identification mark corresponding to the chip test base , the main controller records the usage times of the chip test base according to the identification times of the identification identification sensor. By reasonably setting the maximum number of times of use, when the number of times of use of the chip test base is reached, the main controller will alarm and remind to replace or overhaul the chip test base to ensure the process of chip testing. At the same time, th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com